Note: This PowerPoint presentation contains a significant amount of animation to help illustrate the concepts described. SHARE proceedings are usually restricted to Adobe portable-document-format (.pdf) files. If you would like a copy of the original PowerPoint slide show, please see me after the session or send me an email at the address on the cover page.

This presentation reviews the new CPU facilities introduced (mostly) by the IBM zEnterprise 196 series of processors (the one exception is the message-security-assist extension 3 [MSA-X3] which was introduced in the System z10 GA3 machines, but was not previously published).

The major focus is on general instructions used by various high-level languages such as C and Java. The final slides will address a few other facilities available for authorized programs.

If you have a PowerPoint version of the presentation, this slide, and the section headings that they designate, contain hyperlinks to the various topics and subtopics. Each slide containing specific information has an "Index" hiperlink in the bottom-right corner that will return you to the next-higher level of information. (Note, SHARE limits their download page to PDFs; if you want the PowerPoint show, see me after the presentation, or send a note to dgreiner@us.ibm.com.)

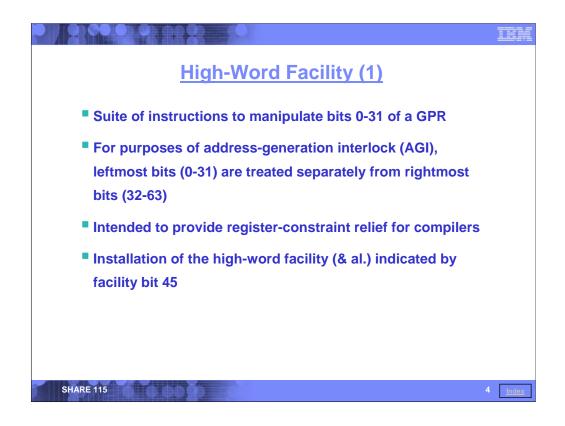

Since its introduction in 1964, System 360 and all of its successors have provided 16 generalpurpose registers. To alleviate the constraint felt by many programmers, numerous architectural features have been added: The relative branching (short and long) facilities, immediate- and extended-immediate-operand facilities, and the long displacement facility are a few examples. However, the 16-register limit continues to prove daunting to both assembler programmers and compiler designers alike.

Although z/Architecture provides 64-bit addressing and arithmetic, many applications continue to operate in the 31-bit addressing mode, and rarely require higher-precision arithmetic than 32 bits. For such programs, the leftmost 32 bits of the 64-bit registers have been of little use ... until now.

The high-word facility provides a means by which selected new instructions can operate on the leftmost 32 bits (bits 0-31) of a general register – independent of the rightmost 32 bits (bits 32-63). This separation extends into address generation performed while in the 24- or 31-bit addressing modes; the updating of the leftmost 32 bits of a general-purpose register, using the high-word instructions, does not affect any pipeline address-generation interlock used by the rightmost 32 bits.

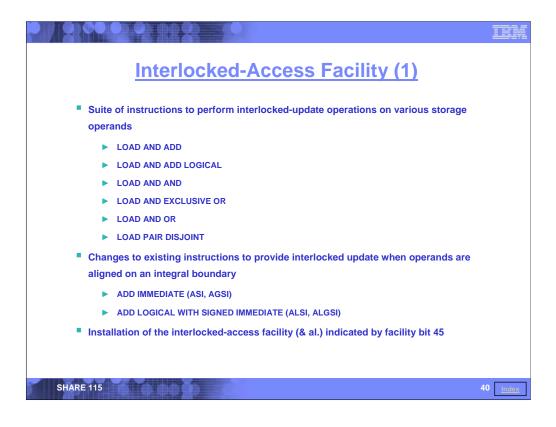

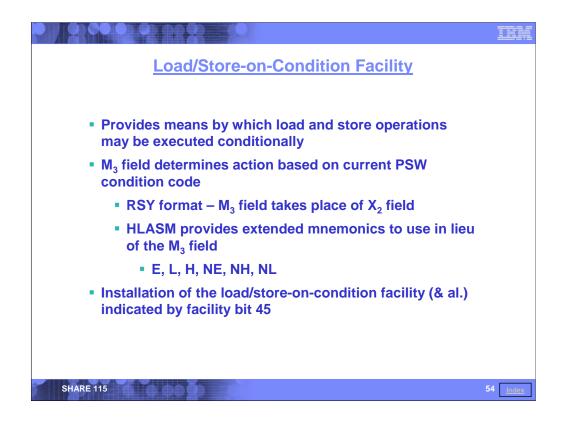

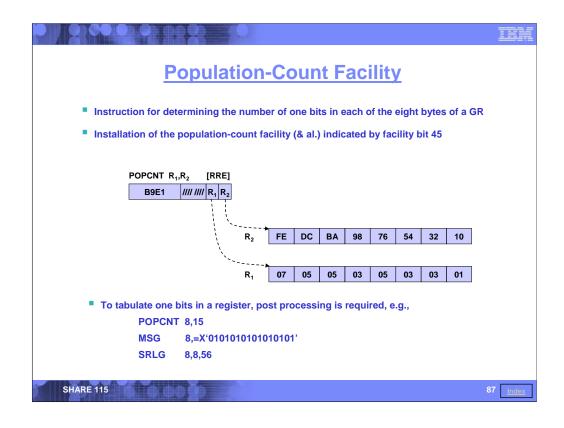

Several of the facilities discussed in this presentation share a common facility bit. Bit 45 indicates the installation of the high-word, interlocked-access, load/store-on-condition, distinct-operands, population-count, and fast-BCR-serialization facilities.

|        |                                                                                             |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                             | 3 <sup>rd</sup> Operand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHHHR  | B9C8                                                                                        | R <sub>1</sub> .0-31                                                                                                  | R <sub>2</sub> .0-31                                                                                                                                                                                                                                                                                                                                                                        | R <sub>3</sub> .0-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AHHLR  | B9D8                                                                                        | R <sub>1</sub> .0-31                                                                                                  | R <sub>2</sub> .0-31                                                                                                                                                                                                                                                                                                                                                                        | R <sub>3</sub> .32-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AIH    | CC8                                                                                         | R <sub>1</sub> .0-31                                                                                                  | I <sub>2</sub> [32 bits]                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ALHHHR | B9CA                                                                                        | R <sub>1</sub> .0-31                                                                                                  | R <sub>2</sub> .0-32                                                                                                                                                                                                                                                                                                                                                                        | R <sub>3</sub> .0-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ALHHLR | B9DA                                                                                        | R <sub>1</sub> .0-31                                                                                                  | R <sub>2</sub> .0-32                                                                                                                                                                                                                                                                                                                                                                        | R <sub>3</sub> .32-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ALSIH  | CCA                                                                                         | R <sub>1</sub> .0-31                                                                                                  | l <sub>2</sub> [32 bits]                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ALSIHN | ССВ                                                                                         | R <sub>1</sub> .0-31                                                                                                  | l <sub>2</sub> [32 bits]                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BRCTH  | CC6                                                                                         | R <sub>1</sub> .0-31                                                                                                  | RI <sub>2</sub> [16 bits]                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CHHR   | B9CD                                                                                        | R <sub>1</sub> .0-31                                                                                                  | R <sub>2</sub> .0-31                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

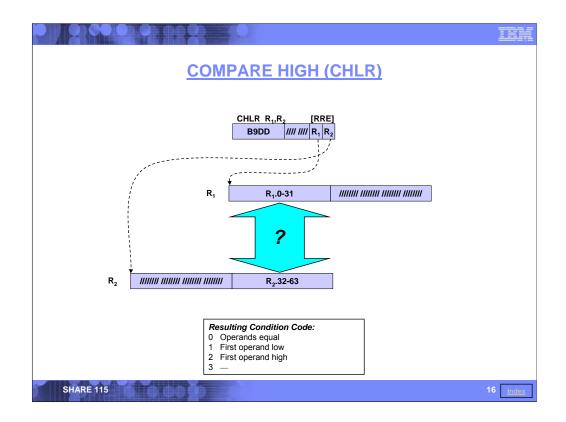

| CHLR   | B9DD                                                                                        | R <sub>1</sub> .0-31                                                                                                  | R <sub>2</sub> .32-63                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

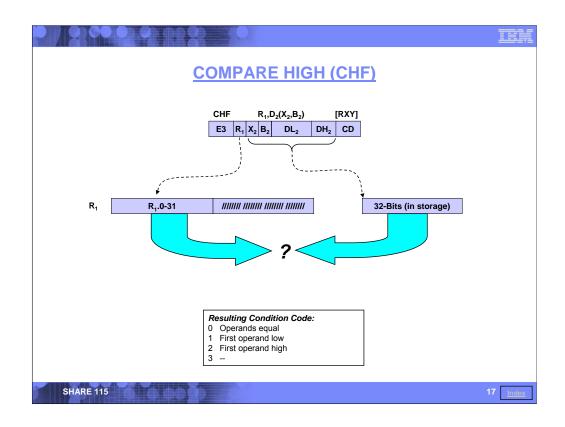

| CHF    | E3CD                                                                                        | R <sub>1</sub> .0-31                                                                                                  | S20 [32 bits]                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

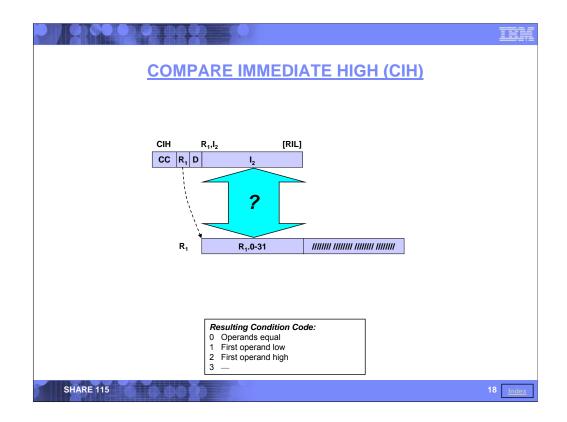

| CIH    | CCD                                                                                         | R <sub>1</sub> .0-31                                                                                                  | I <sub>2</sub> [32 bits]                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        | AHHLR<br>AIH<br>ALHHHR<br>ALHHHR<br>ALSIH<br>ALSIH<br>ALSIH<br>BRCTH<br>CHHR<br>CHLR<br>CHE | AHHLR B9D8   AIH CC8   ALHHR B9CA   ALHHR B9DA   ALSIH CCA   ALSIH CCB   BRCTH CC6   CHHR B9CD   CHLR B9DD   CHE E3CD | AHHLR     B9D8     R, 0-31       AIH     CC8     R, 0-31       ALHHR     B9CA     R, 0-31       ALHHR     B9DA     R, 0-31       ALHHR     B9DA     R, 0-31       ALHHR     B9DA     R, 0-31       ALSIH     CCA     R, 0-31       ALSIH     CCB     R, 0-31       BRCTH     CC6     R, 0-31       CHHR     B9CD     R, 0-31       CHLR     B9DD     R, 0-31       CHE     E3CD     R, 0-31 | AHHLR     B9D8     R <sub>1</sub> .0-31     R <sub>2</sub> .0-31       AIH     CC8     R <sub>1</sub> .0-31     I <sub>2</sub> [32 bits]       ALHHR     B9CA     R <sub>1</sub> .0-31     R <sub>2</sub> .0-32       ALHHR     B9DA     R <sub>1</sub> .0-31     R <sub>2</sub> .0-32       ALHHR     B9DA     R <sub>1</sub> .0-31     R <sub>2</sub> .0-32       ALHHR     B9DA     R <sub>1</sub> .0-31     R <sub>2</sub> .0-32       ALSIH     CCA     R <sub>1</sub> .0-31     I <sub>2</sub> [32 bits]       ALSIH     CCB     R <sub>1</sub> .0-31     I <sub>2</sub> [32 bits]       BRCTH     CC6     R <sub>1</sub> .0-31     R <sub>12</sub> [16 bits]       CHHR     B9CD     R <sub>1</sub> .0-31     R <sub>2</sub> .0-31       CHLR     B9DD     R <sub>1</sub> .0-31     R <sub>2</sub> .32-63       CHE     E3CD     R <sub>1</sub> .0-31     S20 [32 bits] |

This slide enumerates the first 12 instructions in the high-word facility; the remainder are listed on the following slide. As will be immediately obvious, only a limited subset of the instructions are provided to manipulate the high words: ADD, ADD LOGICAL, BRANCH RELATIVE ON COUNT, COMPARE, COMPARE LOGICAL, LOAD BYTE, LOAD HALFWORD, LOAD, LOAD LOGICAL CHARACTER, LOAD LOGICAL HALFWORD, ROTATE THEN INSERT SELECTED BITS, STORE CHARACTER, STORE HALFWORD, STORE, SUBTRACT and SUBTRACT LOGICAL.

Note that many of the arithmetic-operand instructions have distinct operands; that is, the target register is separate from the two source registers.

Also note that, of necessity, certain characters in the mnemonics have become a bit overloaded. The rookie programmer will likely find using the high-word facility challenging. We hope the benefits will be worth it.

| High-V                                | Vord          | Faci   | <u>lity (3):</u>                                       |                          |                                                  |

|---------------------------------------|---------------|--------|--------------------------------------------------------|--------------------------|--------------------------------------------------|

| Instruction                           | Mnemonic      | OpCode | 1 <sup>st</sup> Operand                                | 2 <sup>nd</sup> Operand  | Other                                            |

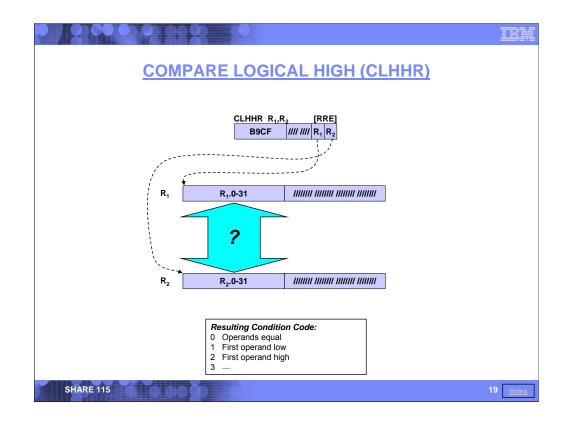

| COMPARE LOGICAL HIGH                  | CLHHR         | B9CF   | R₁.0-31                                                | R <sub>2</sub> .0-31     | _                                                |

| COMPARE LOGICAL HIGH                  | CLHLR         | B9DF   | R <sub>1</sub> .0-31                                   | R <sub>2</sub> .32-63    | _                                                |

| COMPARE LOGICAL HIGH                  | CLHF          | E3CF   | R <sub>1</sub> .0-31                                   | S20 [32 bits]            | _                                                |

| COMPARE LOGICAL IMMEDIATE HIGH        | CLIH          | CCF    | R <sub>1</sub> .0-31                                   | l <sub>2</sub> [32 bits] | _                                                |

| LOAD BYTE HIGH                        | LBH           | E3C0   | R <sub>1</sub> .24-31                                  | S20 [8 BITS]             | _                                                |

| LOAD HALFWORD HIGH                    | LHH           | E3C4   | R <sub>1</sub> .16-31                                  | S20 [16 bits]            | _                                                |

| LOAD HIGH                             | LFH           | E3CA   | R <sub>1</sub> .0-31                                   | S20 [32 bits]            | -                                                |

| LOAD LOGICAL CHARACTER HIGH           | LLCH          | E3C2   | R <sub>1</sub> .24-31                                  | S20 [8 bits]             | _                                                |

| LOAD LOGICAL HALFWORD HIGH            | LLHH          | E3C6   | R <sub>1</sub> .16-31                                  | S20 [16 bits]            | -                                                |

| ROTATE THEN INSERT SELECTED BITS HIGH | RISBHG        | EC5D   | R <sub>1</sub> .I <sub>3</sub> -I <sub>4</sub>         | R <sub>2</sub> .0-63     | l <sub>3</sub> , l <sub>4</sub> , l <sub>5</sub> |

| ROTATE THEN INSERT SELECTED BITS LOW  | RISBLG        | EC51   | R <sub>1</sub> .32+I <sub>3:</sub> - 32+I <sub>4</sub> | R <sub>2</sub> .0-63     | l <sub>3</sub> , l <sub>4</sub> , l <sub>5</sub> |

| STORE CHARACTER HIGH                  | STCH          | E3C3   | R <sub>1</sub> .24-31                                  | S20 [8 bits]             | _                                                |

| STORE HALFWORD HIGH                   | <u>STHH</u>   | E3C7   | R <sub>1</sub> .16-31                                  | S20 [16 bits]            | _                                                |

| STORE HIGH                            | STFH          | E3CB   | R <sub>1</sub> .0-31                                   | S20 [32 bits]            | -                                                |

| SUBTRACT HIGH                         | <u>SHHHR</u>  | B9C9   | R <sub>1</sub> .0-31                                   | R <sub>2</sub> .0-31     | R <sub>3</sub> .0-31                             |

| SUBTRACT HIGH                         | SHHLR         | B9D9   | R <sub>1</sub> .0-31                                   | R <sub>2</sub> .0-31     | R <sub>3</sub> .32-63                            |

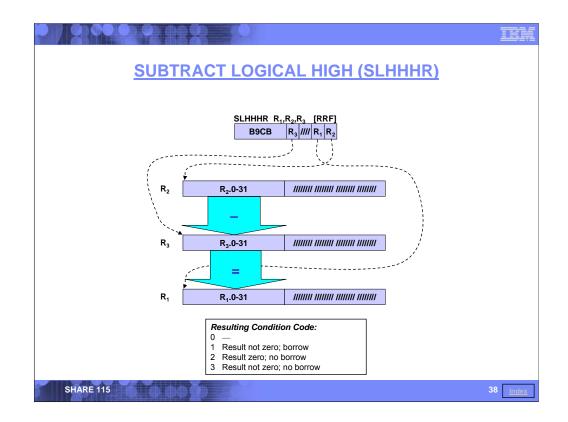

| SUBTRACT LOGICAL HIGH                 | <u>SLHHHR</u> | B9CB   | R <sub>1</sub> .0-31                                   | R <sub>2</sub> .0-31     | R <sub>3</sub> .0-31                             |

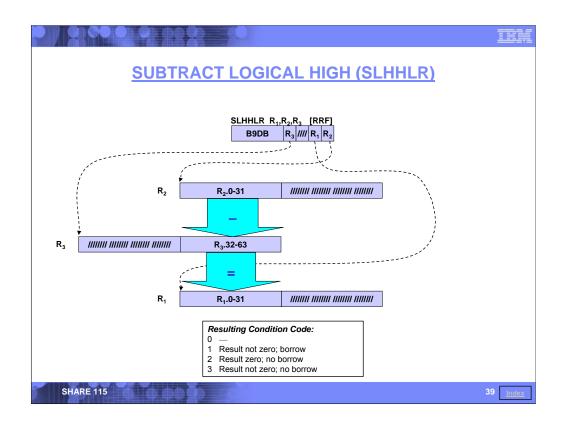

| SUBTRACT LOGICAL HIGH                 | SLHHLR        | B9DB   | R <sub>1</sub> .0-31                                   | R <sub>2</sub> .0-31     | R <sub>3</sub> .32-63                            |

This slide lists the remaining 18 instructions in the high-word facility, for a total of 30 instructions.

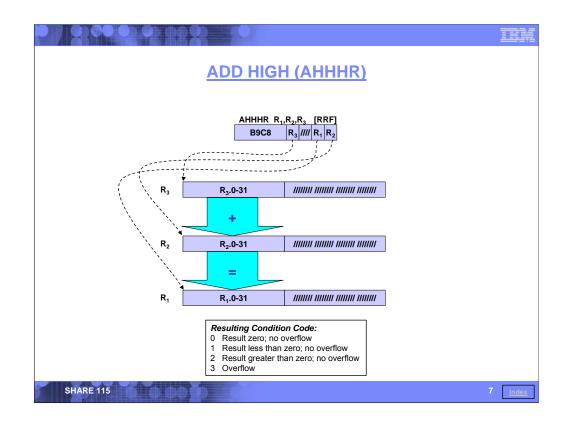

For ADD HIGH (AHHHR), the contents of the leftmost bits (0-31) of the general register designated by the  $R_3$  field of the instruction are added to the contents of the leftmost bits of the general register designated by the  $R_2$  field of the instruction. The results of the addition replace the leftmost bits of the general register remain unchanged.

The addition proceeds exactly as for ADD (AR), except that there are two source operands and a separate target operand – and, obviously, the result ends up in the left of the register.

The condition code is set as with any other signed addition operation.

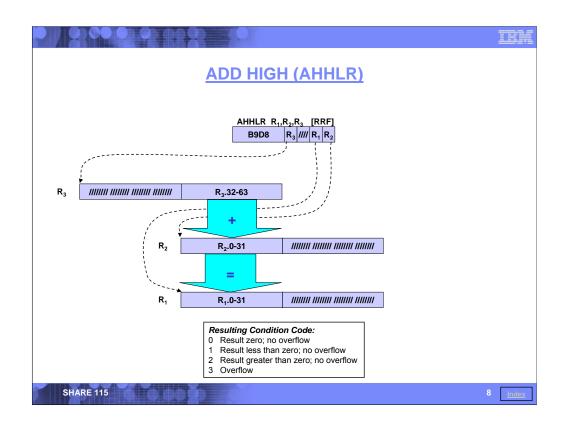

ADD HIGH (AHHLR) should perhaps be called ADD HIGH AND LOW.

The contents of the rightmost bits (32-63) of the general register designated by the  $R_3$  field of the instruction are added to the contents of the leftmost bits (0-31) of the general register designated by the  $R_2$  field of the instruction. The results of the addition replace the leftmost bits of the general register designated by the  $R_1$  operand; bits 32-63 of the result register remain unchanged.

The condition code is set as with any other signed addition operation.

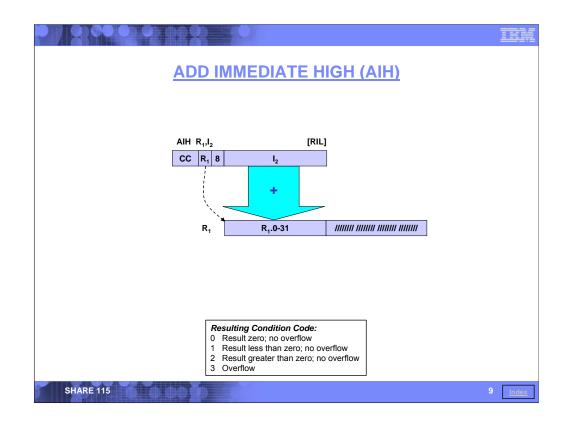

ADD IMMEDIATE HIGH (AIH) adds the contents of the 32-bit signed  $I_2$  field (bits 16-47 of the instruction) with the contents of the leftmost bits (0-31) of the general register designated by the  $R_1$  field of the instruction. The results of the addition replace the leftmost bits of the general register designated by the  $R_1$  operand; bits 32-63 of the result register remain unchanged.

Unlike ADD HIGH (AHHHR and AHHLR), the result replaces the leftmost bits of the first-operand register.

The condition code is set as with any other signed addition operation.

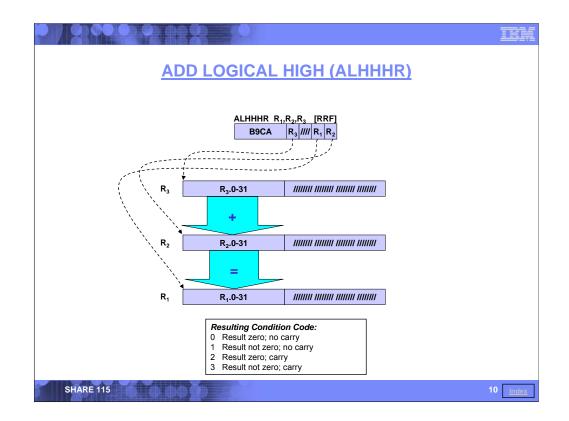

For ADD LOGICAL HIGH (ALHHHR), the contents of the leftmost bits (0-31) of the general register designated by the  $R_3$  field of the instruction are added to the contents of the leftmost bits of the general register designated by the  $R_2$  field of the instruction. The results of the addition replace the leftmost bits of the general register designated by the  $R_1$  field of the instruction; bits 32-63 of the result register remain unchanged.

The addition proceeds exactly as for ADD LOGICAL (ALR), except that there are two source operands and a separate target operand – and, obviously, the result ends up in the left of the register.

The condition code is set as with any other unsigned addition operation.

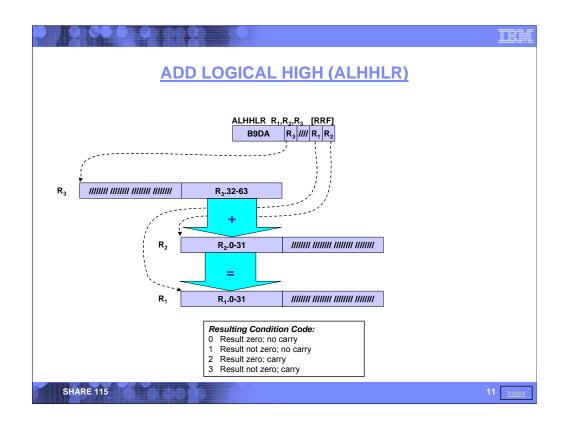

As with ADD HIGH (AHHLR), ADD LOGICAL HIGH (ALHHLR) should perhaps be called ADD LOGICAL HIGH AND LOW.

The contents of the rightmost bits (32-63) of the general register designated by the  $R_3$  field of the instruction are added to the contents of the leftmost bits (0-31) of the general register designated by the  $R_2$  field of the instruction. The results of the addition replace the leftmost bits of the general register designated by the  $R_1$  operand; bits 32-63 of the result register remain unchanged.

The condition code is set as with any other unsigned addition operation.

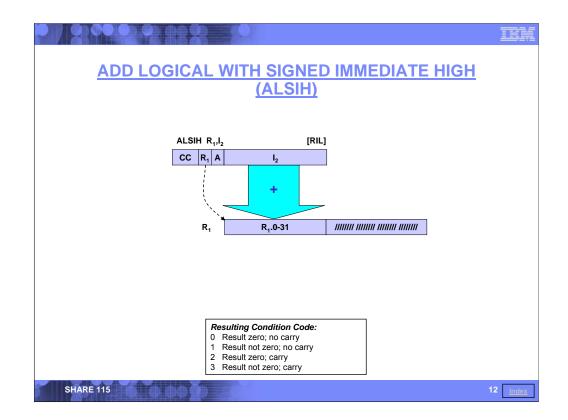

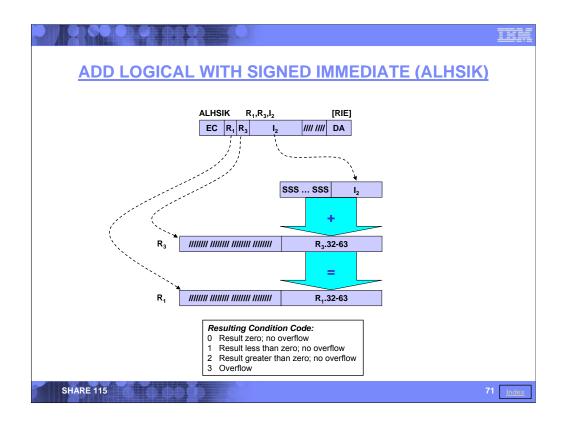

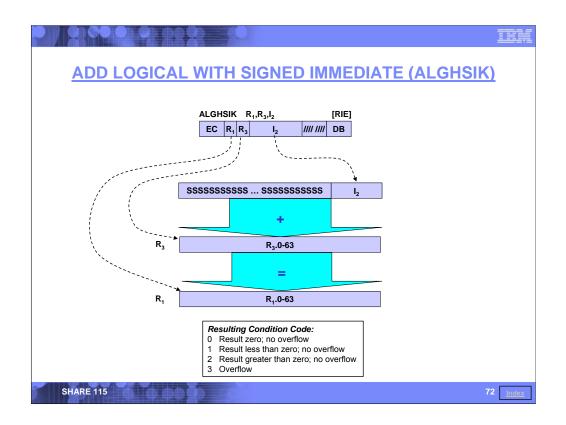

ADD LOGICAL WITH SIGNED IMMEDIATE HIGH (ALSIH) adds the contents of the 32-bit signed  $I_2$  field (bits 16-47 of the instruction) with the contents of the leftmost <u>unsigned</u> bits (0-31) of the general register designated by the  $R_1$  field of the instruction. The results of the addition replace the leftmost bits of the general register designated by the  $R_1$  operand; bits 32-63 of the result register remain unchanged.

As with ADD IMMEDIATE HIGH, the result replaces the leftmost bits of the first-operand register.

The condition code is set as with any other unsigned addition operation!! Although having the second operand be signed reduces the magnitude of the addend by a power of two, it also eliminates the need to define a separate SUBTRACT LOGICAL IMMEDIATE instruction. To subtract, one simply uses a negative second operand.

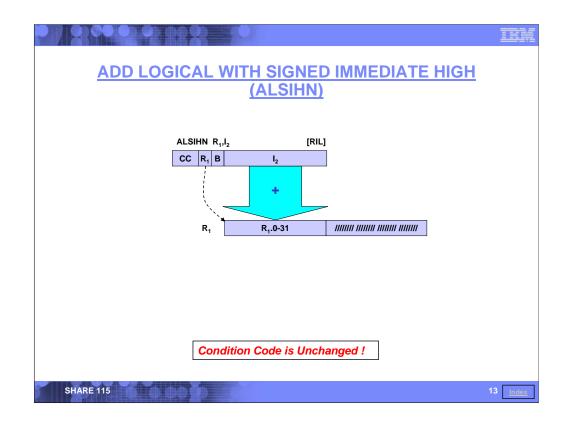

ADD LOGICAL WITH SIGNED IMMEDIATE HIGH (ALSIHN) is identical to ADD LOGICAL WITH SIGNED IMMEDIATE HIGH (ALSIH), except that the condition code remains unchanged.

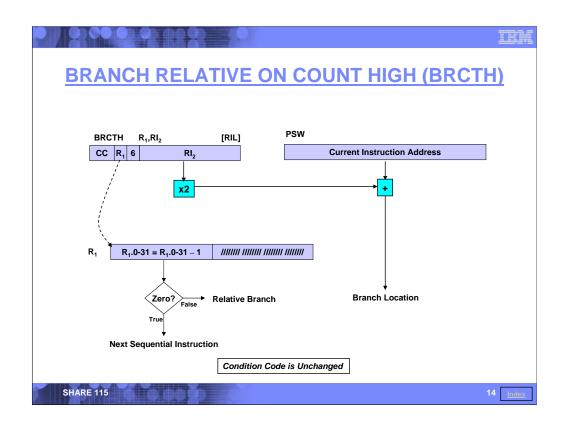

BRANCH RELATIVE ON COUNT HIGH (BRCTH) is an analog to BRANCH RELATIVE AND COUNT (BRCT). BRCTH works identically to BRCT, except that the decremented value (that is, the counter) is in the leftmost bits of the general register designated by the R<sub>1</sub> field of the instruction.

The rightmost 32 bits (32-63) of the counting register and the condition code remain unchanged.

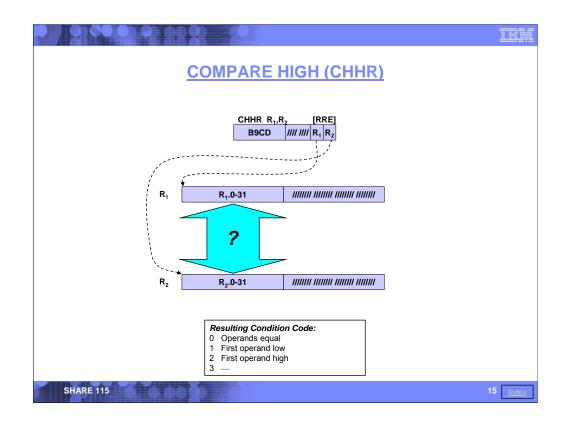

For COMPARE HIGH (CHHR), the contents of the leftmost bits (0-31) of the general register designated by the  $R_2$  field of the instruction are arithmetically compared with the contents of the leftmost bits of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of each register are ignored.

For COMPARE HIGH (CHLR), the contents of the rightmost bits (32-63) of the general register designated by the  $R_2$  field of the instruction are arithmetically compared with the contents of the leftmost bits (0-31) of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of general register  $R_1$  and the leftmost 32 bits of general register  $R_2$  are ignored.

COMPARE HIGH (CHF) is an analog to the COMPARE (C) instruction; the difference being that for CHF, the leftmost 32 bits of the register are compared.

The 32-bit second operand in storage is arithmetically compared with the contents of the leftmost bits of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of general register  $R_1$  are ignored.

COMPARE IMMEDIATE HIGH (CIH) is an analog to the COMPARE IMMEDIATE (CFI) instruction; the difference being that for CIH, the leftmost 32 bits of the register are compared. (CFI was introduced with the general-instruction extension facility in the System z10.)

The 32-bit second immediate field (bits 16-47) of the instruction is arithmetically compared with the contents of the leftmost bits of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of general register  $R_1$  are ignored.

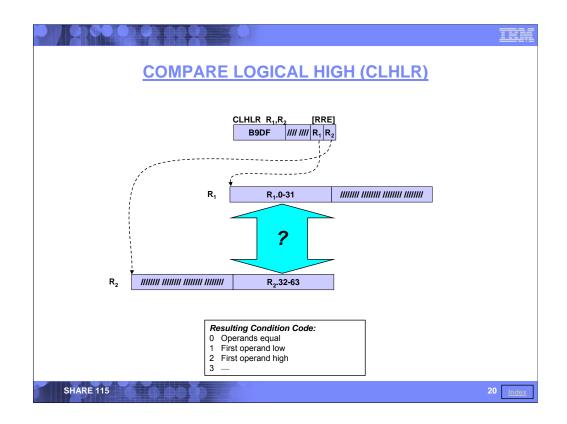

COMPARE LOGICAL HIGH (CLHHR) is an analog to the COMPARE LOGICAL (CLR) instruction; the difference being that for CLHHR, the leftmost 32 bits of the register are compared.

The contents of the leftmost bits (0-31) of the general register designated by the  $R_2$  field of the instruction are logically compared with the contents of the leftmost bits of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of each register are ignored.

For COMPARE LOGICAL HIGH (CLHLR), the contents of the rightmost bits (32-63) of the general register designated by the  $R_2$  field of the instruction are logically compared with the contents of the leftmost bits (0-31) of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of general register  $R_1$  and the leftmost 32 bits of general register  $R_2$  are ignored.

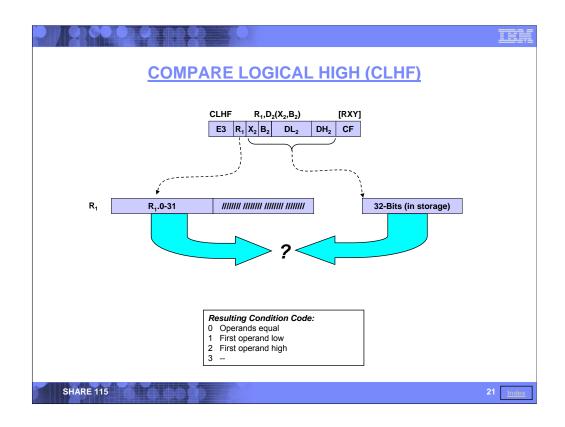

COMPARE LOGICAL HIGH (CLHF) is an analog to the COMPARE LOGICAL (CL) instruction; the difference being that for CLHF, the leftmost 32 bits of the register are compared.

The 32-bit second operand in storage is logically compared with the contents of the leftmost bits of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of general register  $R_1$  are ignored.

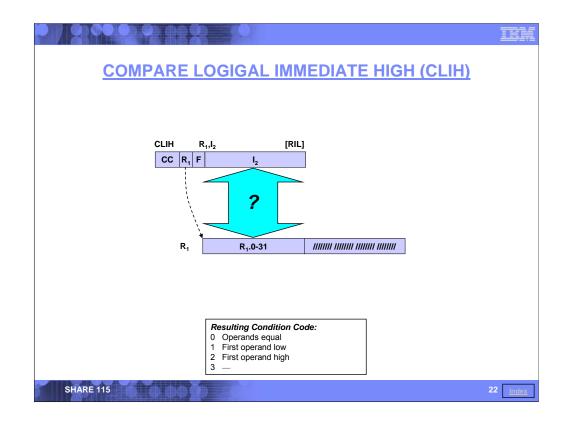

COMPARE LOGICAL IMMEDIATE HIGH (CLIH) is an analog to the COMPARE LOGICAL IMMEDIATE (CLFI) instruction; the difference being that for CLIH, the leftmost 32 bits of the register are compared. (CLFI was introduced with the general-instructions extension facility in the System z10.)

The 32-bit second immediate field (bits 16-47) of the instruction is logically compared with the contents of the leftmost bits of the general register designated by the  $R_1$  field of the instruction. The rightmost 32 bits of general register  $R_1$  are ignored.

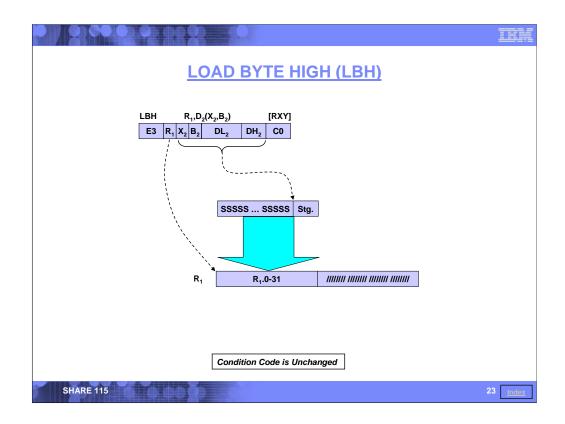

LOAD BYTE HIGH (LBH) is the analog to the LOAD BYTE (LB), except that the results are placed in the leftmost bits of the first-operand register. (LOAD BYTE (LB) was introduced with the long-displacement facility in the z990.)

The byte in storage designated by the second-operand location is sign extended on the left and the result is placed in bits 0-31 of the general register designated by the  $R_1$  field of the instruction.

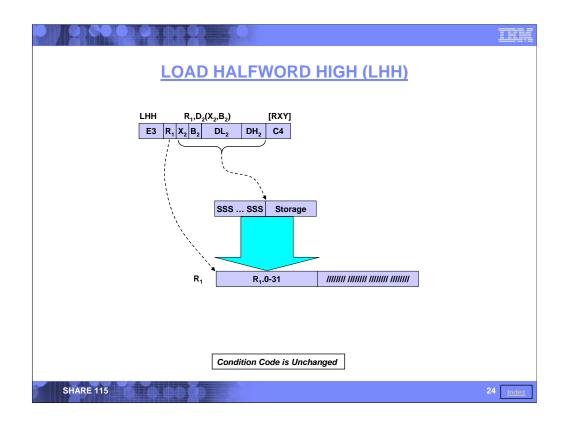

LOAD HALFWORD HIGH (LHH) is the analog to the LOAD HALFWORD (LH), except that the results are placed in the leftmost bits of the first-operand register.

The two-byte field in storage designated by the second-operand location is sign extended on the left and the result is placed in bits 0-31 of the general register designated by the  $R_1$  field of the instruction.

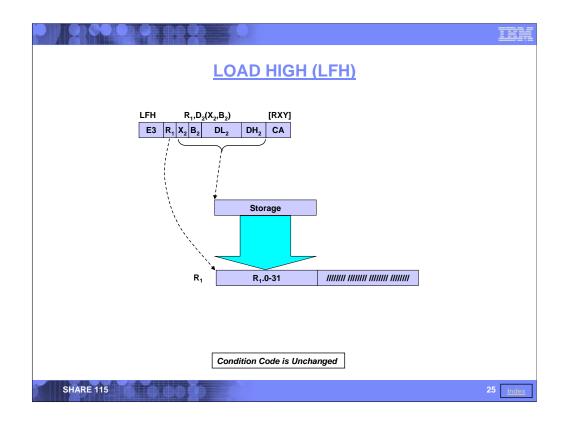

LOAD HIGH (LFH) is the analog to the LOAD (L), except that the results are placed in the leftmost bits of the first-operand register.

The four-byte field in storage designated by the second-operand location is placed in bits 0-31 of the general register designated by the  $R_1$  field of the instruction.

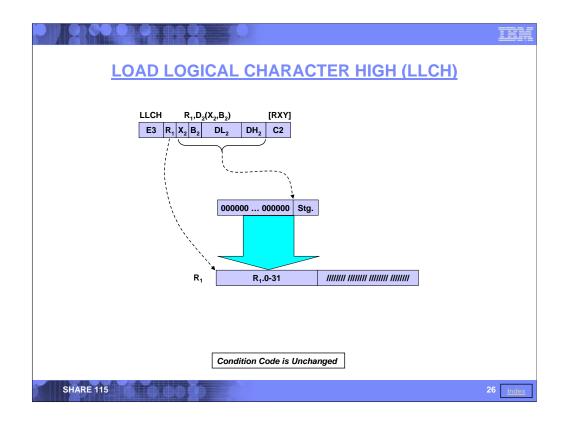

LOAD LOCICAL CHARACTER HIGH (LLCH) is the analog to the LOAD LOGICAL CHARACTER (LLC), except that the results are placed in the leftmost bits of the first-operand register. (LOAD LOGICAL CHARACTER (LLC) was introduced with the extended-immediate facility in the z9-109.)

The byte in storage designated by the second-operand location is zero extended on the left and the result is placed in bits 0-31 of the general register designated by the  $R_1$  field of the instruction.

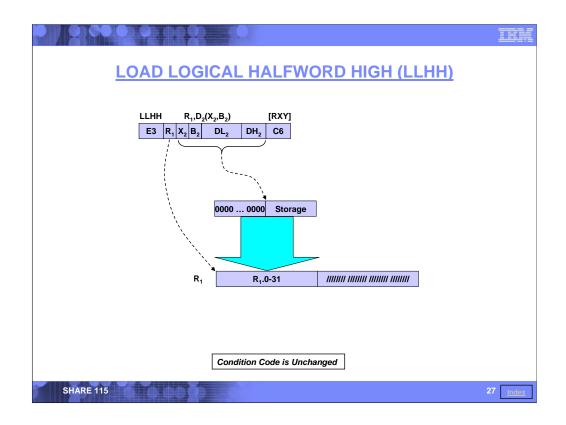

LOAD LOCICAL HALFWORD HIGH (LLHH) is the analog to the LOAD LOGICAL HALFWORD (LLH), except that the results are placed in the leftmost bits of the first-operand register. (LOAD LOGICAL HALFWORD (LLH) was introduced with the extended-immediate facility in the z9-109.)

The two bytes in storage designated by the second-operand location are zero extended on the left and the result is placed in bits 0-31 of the general register designated by the  $R_1$  field of the instruction.

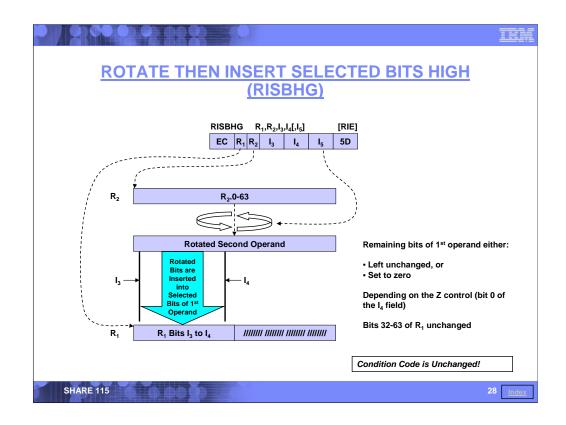

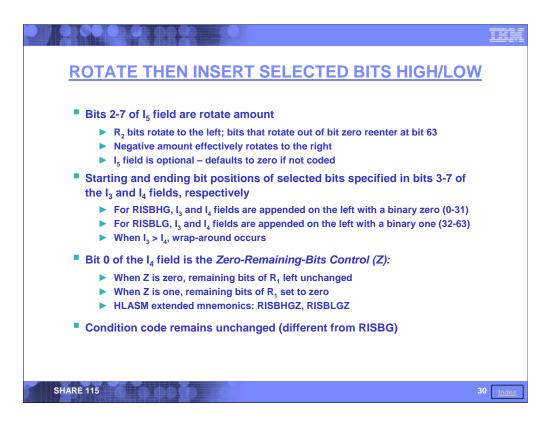

ROTATE THEN INSERT SELECTED BITS HIGH (RISBHG) is the analog to ROTATE THEN INSERT SELECTED BITS (RISBG), except that the results of RISBHG are limited to the leftmost bits of general register  $R_1$ . Note ROTATE THEN INSERT SELECTED BITS (RISBG) was introduced with the general-instructions enhancement facility on the System z10.

All 64 bits of the second operand are rotated to the left by the number of bits specified in the fifth operand (note, if the fifth operand is coded as a negative value, the rotation appears to occur to the right).

The  $I_3$  and  $I_4$  fields of the instruction are used to specify a starting and ending bit position in the result register (that is, the general register designated by the  $R_1$  field of the instruction). The selected bits of the rotated second operand are inserted into the corresponding bits of the result register.

The remaining bits of the leftmost 32 bits of the result register are either left unchanged or set to zeros, depending on whether the zero-remaining-bits control (bit 0 of the  $I_3$  field of the instruction) is zero or one, respectively.

Unless the  $R_1$  and  $R_2$  fields designate the same register, the general register designated by the  $R_2$  field of the instruction remains unchanged. The rightmost 32 bits of the general register designated by the  $R_1$  field always remain unchanged.

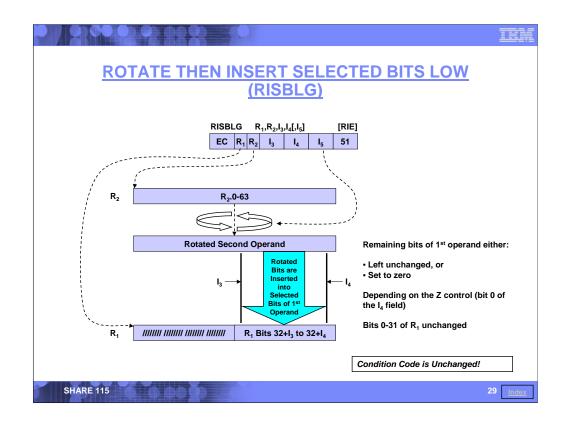

ROTATE THEN INSERT SELECTED BITS LOW (RISBLG) is the analog to ROTATE THEN INSERT SELECTED BITS (RISBG), except that the results of RISBLG are limited to the rightmost bits of general register  $R_1$ . Note ROTATE THEN INSERT SELECTED BITS (RISBG) was introduced with the general-instructions enhancement facility on the System z10.

All 64 bits of the second operand are rotated to the left by the number of bits specified in the fifth operand (note, if the fifth operand is coded as a negative value, the rotation appears to occur to the right).

The  $I_3$  and  $I_4$  fields of the instruction are used to specify a starting and ending bit position in the rightmost 32 bits of the result register (that is, the general register designated by the  $R_1$  field of the instruction). Although the values of the  $I_3$  and  $I_4$  fields are each encoded in a range of 0-31, the effective bit positions in the 64-bit register are 32 bits higher. The selected (rightmost 32) bits of the rotated second operand are inserted into the corresponding (rightmost 32) bits of the result register.

The remaining bits of the rightmost 32 bits of the result register are either left unchanged or set to zeros, depending on whether the zero-remaining-bits control (bit 0 of the  $I_3$  field of the instruction) is zero or one, respectively.

Unless the  $R_1$  and  $R_2$  fields designate the same register, the general register designated by the  $R_2$  field of the instruction remains unchanged. The leftmost 32 bits of the general register designated by the  $R_1$  field always remain unchanged.

Note that for RISBHG, the  $I_3$  and  $I_4$  fields directly designate bits 0-31 of the result register. For RISBLG, a binary one is implicitly appended to the left of the values coded in the  $I_3$  and  $I_4$  fields, thus the effective bit positions in the result register are 32-63.

Unlike ROTATE THEN INSERT SELECTED BITS (RISBG), the ROTATE THEN INSERT SELECTED BITS HIGH / LOW instructions do not set the condition code. This allows the instructions to be used to implement pseudo-instructions (see the next slide).

| Instruction Name                   | Extended M | Inemonic                       | RISBHG / RISBLG Equi |                                          |

|------------------------------------|------------|--------------------------------|----------------------|------------------------------------------|

| LOAD (HIGH←HIGH)                   | LHHR       | R <sub>1</sub> ,R <sub>2</sub> | RISBHGZ              | R <sub>1</sub> ,R <sub>2</sub> ,0,31     |

| LOAD (HIGH←LOW)                    | LHLR       | R <sub>1</sub> ,R <sub>2</sub> | RISBHGZ              | R <sub>1</sub> ,R <sub>2</sub> ,0,31,32  |

| LOAD (LOW←HIGH)                    | LLHFR      | R <sub>1</sub> ,R <sub>2</sub> | RISBLGZ              | R <sub>1</sub> ,R <sub>2</sub> ,0,31,32  |

| LOAD LOGICAL HALFWORD (HIGH←HIGH)  | LLHHHR     | R <sub>1</sub> ,R <sub>2</sub> | RISBHGZ              | R <sub>1</sub> ,R <sub>2</sub> ,16,31    |

| LOAD LOGICAL HALFWORD (HIGH←LOW)   | LLHHLR     | R <sub>1</sub> ,R <sub>2</sub> | RISBHGZ              | R <sub>1</sub> ,R <sub>2</sub> ,16,31,32 |

| LOAD LOGICAL HALFWORD (LOW-HIGH)   | LLHLHR     | R <sub>1</sub> ,R <sub>2</sub> | RISBLGZ              | R <sub>1</sub> ,R <sub>2</sub> ,16,31,32 |

| LOAD LOGICAL CHARACTER (HIGH←HIGH) | LLCHHR     | R <sub>1</sub> ,R <sub>2</sub> | RISBHGZ              | R <sub>1</sub> ,R <sub>2</sub> ,24,31    |

| LOAD LOGICAL CHARACTER (HIGH←LOW)  | LLCHLR     | R <sub>1</sub> ,R <sub>2</sub> | RISBHGZ              | R <sub>1</sub> ,R <sub>2</sub> ,24,31,32 |

| LOAD LOGICAL CHARACTER (LOW←HIGH)  | LLCLHR     | R1,R2                          | RISBLGZ              | R <sub>1</sub> ,R <sub>2</sub> ,24,31,32 |

With ROTATE THEN INSERT SELECTED BITS HIGH and ROTATE THEN INSERT SELECTED BITS LOW, a large group of other pseudo-instructions can be implemented, as illustrated on this slide.

The High-Level Assembler provides extended mnemonics that implement these pseudo-instructions, even though they are actually implemented with RISBHG and RISBLG.

| Instruction Name         | Extende | ed Mnemonic                    | R*SBG Equivalent |                                         |

|--------------------------|---------|--------------------------------|------------------|-----------------------------------------|

| AND HIGH (HIGH←HIGH)     | NHHR    | R <sub>1</sub> ,R <sub>2</sub> | RNSBG            | R <sub>1</sub> ,R <sub>2</sub> ,0,31    |

| AND HIGH (HIGH←LOW)      | NHLR    | R <sub>1</sub> ,R <sub>2</sub> | RNSBG            | R <sub>1</sub> ,R <sub>2</sub> ,0,31,32 |

| AND HIGH (LOW←HIGH)      | NLHR    | R <sub>1</sub> ,R <sub>2</sub> | RNSBG            | R <sub>1</sub> ,R <sub>2</sub> ,32,63,3 |

| EXCLUSIVE OR (HIGH←HIGH) | XHHR    | R <sub>1</sub> ,R <sub>2</sub> | RXSBG            | R <sub>1</sub> ,R <sub>2</sub> ,0,31    |

| EXCLUSIVE OR (HIGH←LOW)  | XHLR    | R <sub>1</sub> ,R <sub>2</sub> | RXSBG            | R <sub>1</sub> ,R <sub>2</sub> ,0,31,32 |

| EXCLUSIVE OR (LOW←HIGH)  | XLHR    | R <sub>1</sub> ,R <sub>2</sub> | RXSBG            | R <sub>1</sub> ,R <sub>2</sub> ,32,63,3 |

| OR (HIGH←HIGH)           | OHHR    | R <sub>1</sub> ,R <sub>2</sub> | ROSBG            | R <sub>1</sub> ,R <sub>2</sub> ,0,31    |

| OR (HIGH←LOW)            | OHLR    | R <sub>1</sub> ,R <sub>2</sub> | ROSBG            | R <sub>1</sub> ,R <sub>2</sub> ,0,31,32 |

| OR (LOW←HIGH)            | OLHR    | R <sub>1</sub> ,R <sub>2</sub> | ROSBG            | R <sub>1</sub> ,R <sub>2</sub> ,32,63,3 |

The High-Level Assembler also provides pseudo-instructions to perform high-word logical operations by using the ROTATE THEN AND SELECTED BITS, ROTATE THEN OR SELECTED BITS, and ROTATE THEN EXCLUSIVE OR SELECTED BITS instructions (RNSBG, ROSBG, and RXSBG were introduced with the System z10).

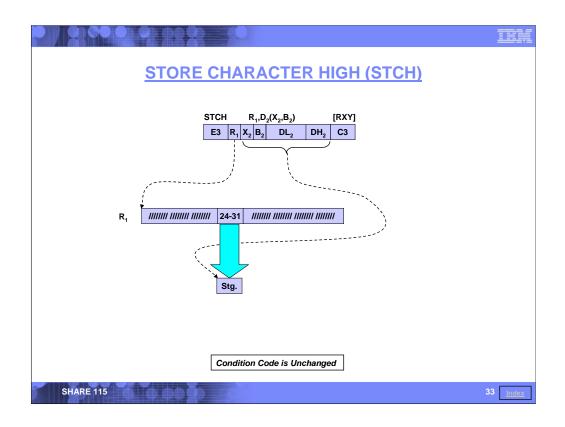

STORE CHARACTER HIGH (STCH) is the analog to STORE CHARACTER (STC), except that the byte stored is in bits 24-31 of the general register designated by the R<sub>1</sub> field of the instruction.

Bits 24-31 of general register  $R_1$  are placed into the byte in storage designated by the second-operand location.

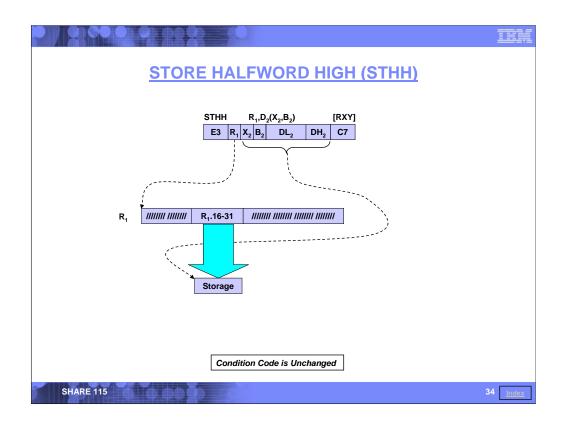

STORE HALFWORD HIGH (STHH) is the analog to STORE HALFWORD (STH), except that the two bytes stored are in bits 16-31 of the general register designated by the R<sub>1</sub> field of the instruction.

Bits 16-31 of general register  $R_1$  are placed into the two bytes in storage designated by the second-operand location.

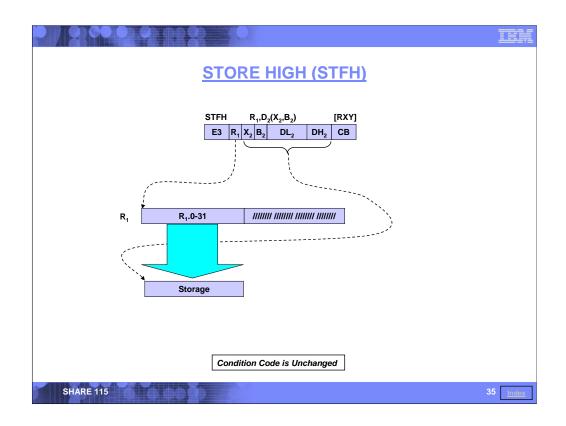

STORE HIGH (STFH) is the analog to STORE (ST), except that the four bytes stored are in bits 0-31 of the general register designated by the  $R_1$  field of the instruction.

Bits 0-31 of general register  $R_1$  are placed into the four bytes in storage designated by the second-operand location.

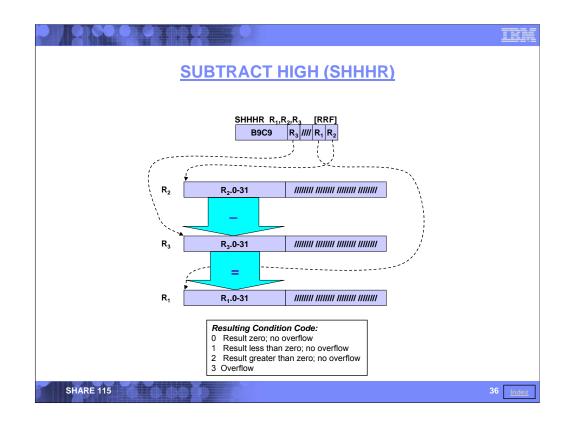

For SUBTRACT HIGH (SHHHR), the contents of the leftmost bits (0-31) of the general register designated by the  $R_3$  field of the instruction are arithmetically subtracted from the contents of the leftmost bits of the general register designated by the  $R_2$  field of the instruction. The difference replaces the leftmost bits of the general register designated by the  $R_1$  field of the instruction; bits 32-63 of the result register remain unchanged.

The subtraction proceeds exactly as for SUBTRACT (SR), except that there are two source operands and a separate target operand – and, obviously, the result ends up in the leftmost 32 bits of the register.

The condition code is set as with any other signed subtraction operation.

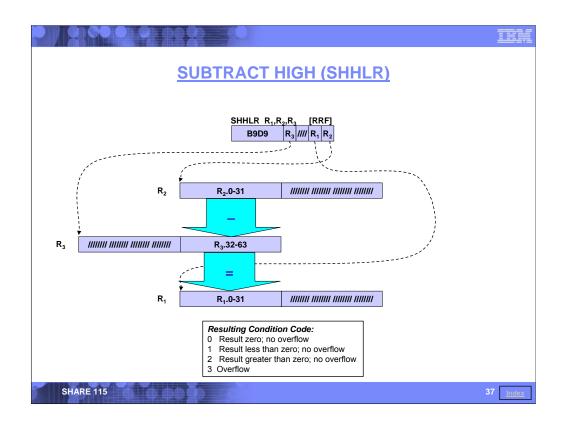

SUBTRACT HIGH (SHHLR) should perhaps be called SUBTRACT LOW FROM HIGH.

The contents of the rightmost bits (32-63) of the general register designated by the  $R_3$  field of the instruction are arithmetically subtracted from the contents of the leftmost bits (0-31) of the general register designated by the  $R_2$  field of the instruction. The difference replaces the leftmost bits of the general register designated by the  $R_1$  operand; bits 32-63 of the result register remain unchanged.

The condition code is set as with any other signed addition operation.

For SUBTRACT LOGICAL HIGH (SLHHR), the contents of the leftmost bits (0-31) of the general register designated by the  $R_3$  field of the instruction are logically subtracted from the contents of the leftmost bits of the general register designated by the  $R_2$  field of the instruction. The difference replaces the leftmost bits of the general register designated by the  $R_1$  field of the instruction; bits 32-63 of the result register remain unchanged.

The subtraction proceeds exactly as for SUBTRACT LOGICAL (SLR), except that there are two source operands and a separate target operand – and, obviously, the result ends up in the leftmost 32 bits of the register.

The condition code is set as with any other unsigned addition operation.

As with SUBTRACT HIGH (SHHLR), SUBTRCT LOGICAL HIGH (SLHHLR) should perhaps be called SUBTRACT LOGICAL LOW FROM HIGH.

The contents of the rightmost bits (32-63) of the general register designated by the  $R_3$  field of the instruction are logically subtracted from the contents of the leftmost bits (0-31) of the general register designated by the  $R_2$  field of the instruction. The difference replaces the leftmost bits of the general register designated by the  $R_1$  operand; bits 32-63 of the result register remain unchanged.

The condition code is set as with any other unsigned addition operation.

The interlocked-access facility provides instructions that are designed to facilitate multiprogramming; most of the instructions access memory in a block-concurrent, interlocked-update fashion (more details on the next slides).

Also, when the interlocked-access facility is installed, the ADD IMMEDIATE (ASI and AGSI) and ADD LOGICAL WITH SIGNED IMMEDIATE (ALSI and ALGSI) perform their storage accesses using block-concurrent, interlocked update when the storage operand is aligned on an integral boundary. Thus, as observed by other CPUs and the channel subsystem, the fetch, addition, and store of the result appear to occur atomically ... there is no need for a COMPARE AND SWAP loop to perform these operations!

| .OAD AND ADD<br>.OAD AND ADD<br>.OAD AND ADD LOGICAL | LAA   |      |                       |               | 3 <sup>rd</sup> Operand                          |

|------------------------------------------------------|-------|------|-----------------------|---------------|--------------------------------------------------|

|                                                      |       | EBF8 | R <sub>1</sub> .32-63 | S12 [32 bits] | R <sub>3</sub> .32-63                            |

| OAD AND ADD LOGICAL                                  | LAAG  | EBE8 | R <sub>1</sub> .0-63  | S12 [64 bits] | R <sub>3</sub> .0-63                             |

|                                                      | LAAL  | EBFA | R <sub>1</sub> .32-63 | S12 [32 bits] | R <sub>3</sub> .32-63                            |

| OAD AND ADD LOGICAL                                  | LAALG | EBEA | R <sub>1</sub> .0-63  | S12 [64 bits] | R <sub>3</sub> .0-63                             |

| OAD AND AND                                          | LAN   | EBF4 | R <sub>1</sub> .32-63 | S12 [32 bits] | R <sub>3</sub> .32-63                            |

| OAD AND AND                                          | LANG  | EBE4 | R <sub>1</sub> .0-63  | S12 [64 bits] | R <sub>3</sub> .0-63                             |

| OAD AND EXCLUSIVE OR                                 | LAX   | EBF7 | R <sub>1</sub> .32-63 | S12 [32 bits] | R <sub>3</sub> .32-63                            |

| OAD AND EXCLUSIVE OR                                 | LAXG  | EBE7 | R₁.0-63               | S12 [64 bits] | R <sub>3</sub> .0-63                             |

| OAD AND OR                                           | LAO   | EBF6 | R <sub>1</sub> .32-63 | S12 [32 bits] | R <sub>3</sub> .32-63                            |

| OAD AND OR                                           | LAOG  | EBE6 | R <sub>1</sub> .0-63  | S12 [64 bits] | R <sub>3</sub> .0-63                             |

| OAD PAIR DISJOINT                                    | LPD   | C84  | S12 [32 bits]         | S12 [32 bits] | R <sub>3</sub> .32-63<br>R <sub>3</sub> +1.32-63 |

| OAD PAIR DISJOINT                                    | LPDG  | C85  | S12 [32 bits]         | S12 [32 bits] | R <sub>3</sub> .0-63<br>R <sub>3</sub> +1.0-63   |

- The interlocked-access facility comprises two types of arithmetic operations (signed addition and unsigned addition), and three types of logical operations (AND, OR and XOR). For each of these operations. For each of these five operations, the instruction performs the following:

- 1. The second-operand storage location is fetched.

- An operation is performed using the contents of the third-operand register and the storage location, with the result being placed into the storage location. The access of the storage location (beginning with the fetch in step 1, through the store in this step) is performed as a blockconcurrent, interlocked update (that is, it's atomic).

- 3. The original second-operand value (prior to any modification in step 2) is placed in the firstoperand register.

- The illustrative sequence of the operation shown on the following slides differs somewhat from that described here, however the result is the same.

- The facility also includes an operation to access two discrete storage locations, providing an indication as to whether any other CPU altered one of the locations during the fetch.

For each of these operations, there is a 32-bit and a 64-bit version of the instruction.

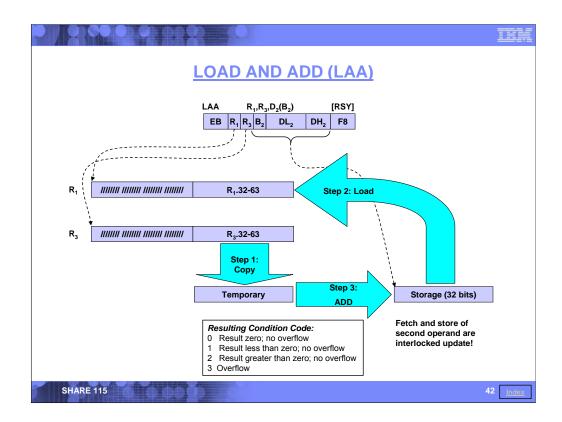

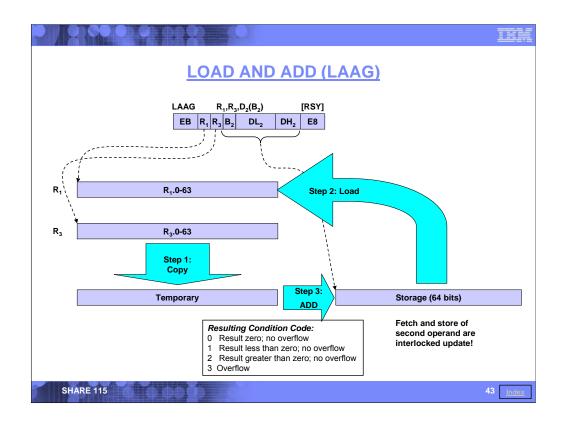

For LOAD AND ADD (LAA), the contents of bits 32-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the word in storage designated by the second-operand location is fetched into bits 32-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 32-bit value is added to the contents of the word in storage, and the result replaces the word in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the word in storage appear to occur as a block-concurrent interlocked update.

Alternatively, the word in storage may be fetched into a temporary location, the addition of that word and general register  $R_3$  occurs, and then the temporary value place in general register  $R_1$ . Regardless of method, the fetching into a temporary location ensures that the result in general register  $R_1$  is the original contents of the storage location (prior to the addition).

For LOAD AND ADD (LAAG), the contents of bits 0-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the doubleword in storage designated by the second-operand location is fetched into bits 0-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 64-bit value is added to the contents of the doubleword in storage, and the result replaces the doubleword in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the doubleword in storage appear to occur as a block-concurrent interlocked update.

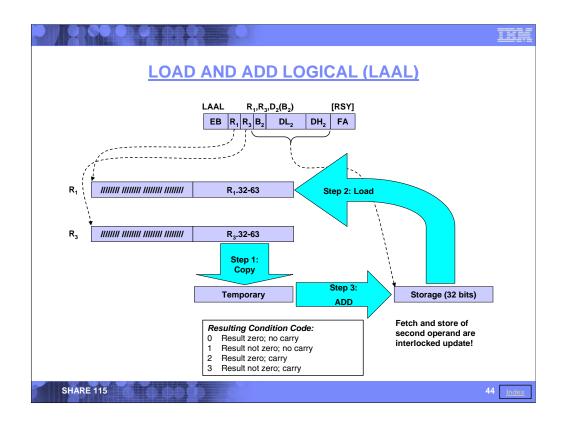

The operation of LOAD AND ADD LOGICAL (LAAL) is identical to that of LOAD AND ADD (LAA), except for the setting of the condition code. LAAL sets the condition code consistent with other unsigned additions.

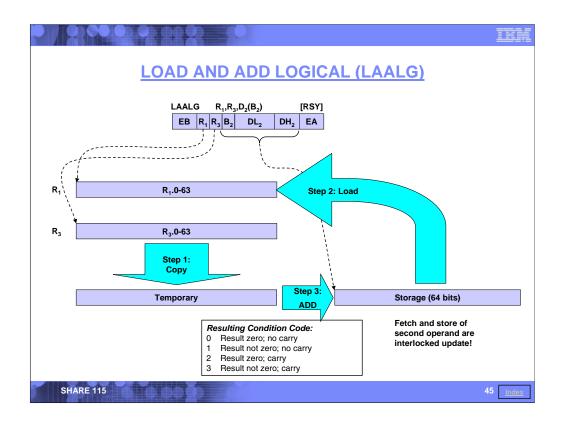

The operation of LOAD AND ADD LOGICAL (LAALG) is identical to that of LOAD AND ADD (LAAG), except for the setting of the condition code. LAALG sets the condition code consistent with other unsigned additions.

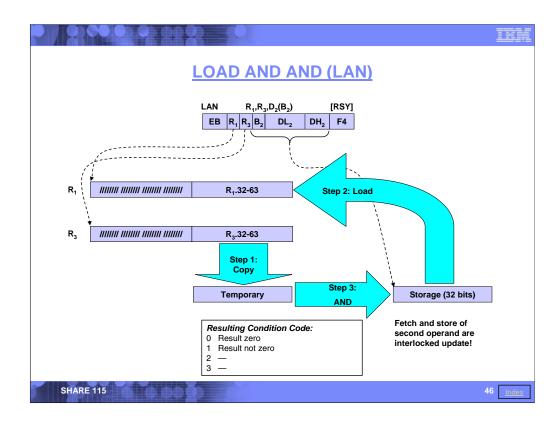

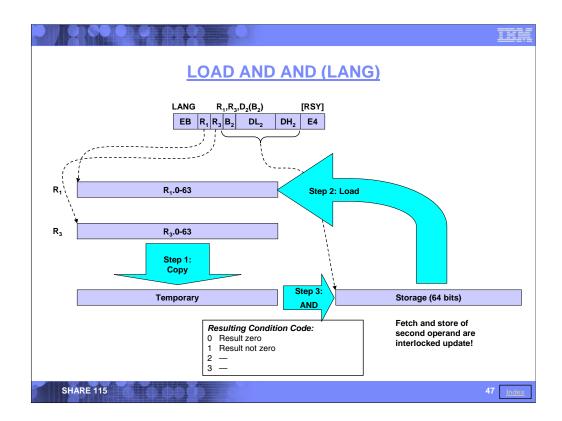

For LOAD AND AND (LAN), the contents of bits 32-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the word in storage designated by the second-operand location is fetched into bits 32-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 32-bit value is logically ANDed with the contents of the word in storage, and the result replaces the word in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the word in storage appear to occur as a block-concurrent interlocked update.

For LOAD AND AND (LANG), the contents of bits 0-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the doubleword in storage designated by the second-operand location is fetched into bits 0-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 64-bit value is logically ANDed with the contents of the doubleword in storage, and the result replaces the doubleword in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the doubleword in storage appear to occur as a block-concurrent interlocked update.

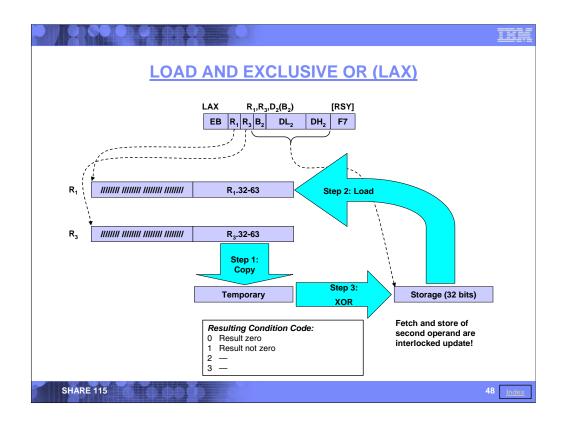

For LOAD AND EXCLUSIVE OR (LAX), the contents of bits 32-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the word in storage designated by the second-operand location is fetched into bits 32-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 32-bit value is logically exclusive ORed with the contents of the word in storage, and the result replaces the word in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the word in storage appear to occur as a block-concurrent interlocked update.

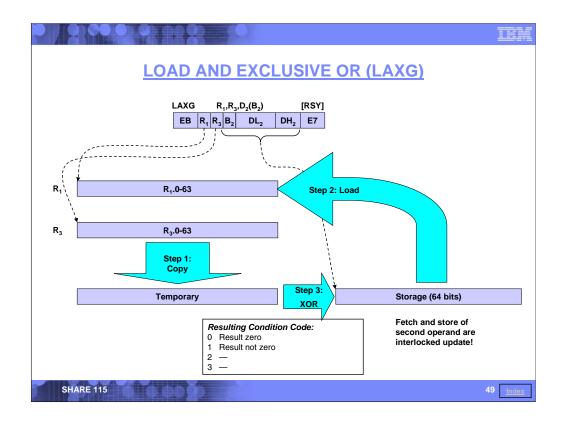

For LOAD AND EXCLUSIVE OR (LAXG), the contents of bits 0-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the doubleword in storage designated by the second-operand location is fetched into bits 0-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 64-bit value is logically exclusive ORed with the contents of the doubleword in storage, and the result replaces the doubleword in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the doubleword in storage appear to occur as a block-concurrent interlocked update.

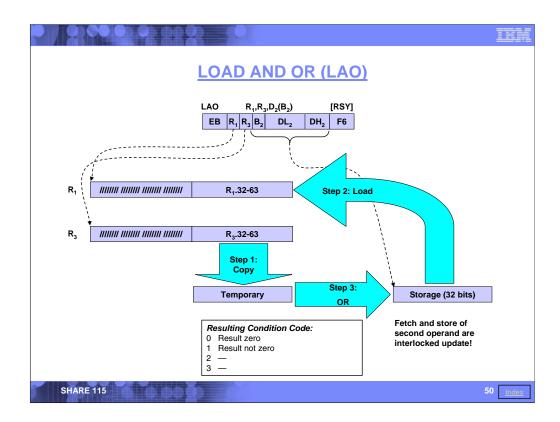

For LOAD AND OR (LAO), the contents of bits 32-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the word in storage designated by the second-operand location is fetched into bits 32-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 32-bit value is logically ORed with the contents of the word in storage, and the result replaces the word in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the word in storage appear to occur as a block-concurrent interlocked update.

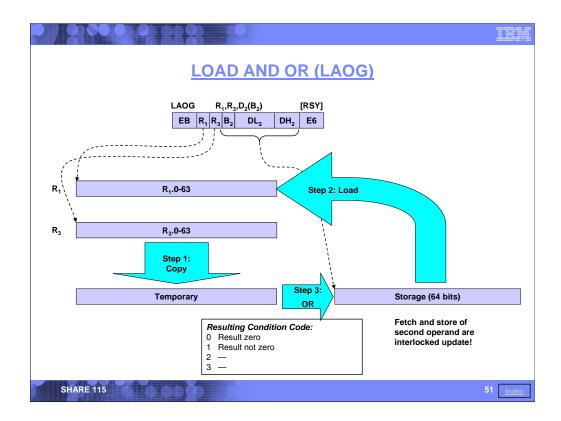

For LOAD AND OR (LAOG), the contents of bits 0-63 of the general register designated by the  $R_3$  field of the instruction are preserved in a temporary location in the CPU. Then the doubleword in storage designated by the second-operand location is fetched into bits 0-63 of the general register designated by the  $R_1$  field of the instruction. Finally, the temporary 64-bit value is logically ORed with the contents of the doubleword in storage, and the result replaces the doubleword in storage. As observed by other CPUs and the channel subsystem, the fetching and storing of the doubleword in storage appear to occur as a block-concurrent interlocked update.

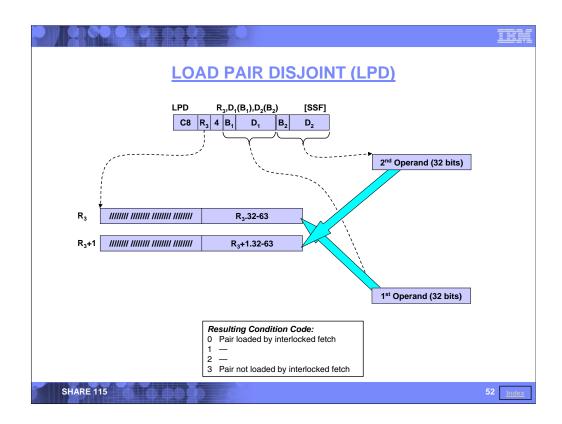

For LOAD PAIR DISJOINT (LPD), the first and second operands are two distinct words in storage. The first and second operands are fetched into bits 32-63 of the even-odd general register pair designated by the  $R_3$  field of the instruction; the first operand is fetched into the even-numbered register, and the second operand is fetched into the odd-numbered register.

The condition code is set based on whether the pair of words were fetched without alteration by other CPUs or the channel subsystem. CC0 means that neither word was altered during the fetching; CC3 means that one of the words was altered.

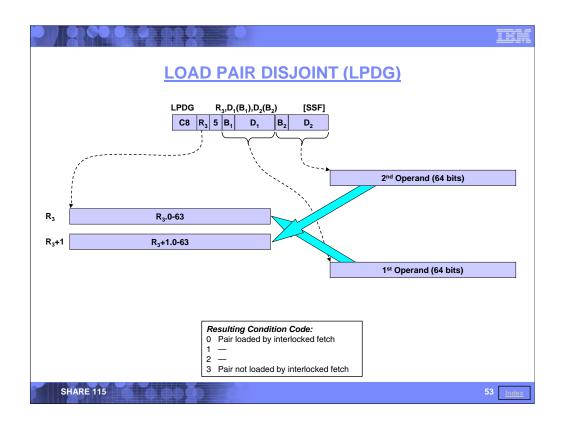

For LOAD PAIR DISJOINT (LPDG), the first and second operands are two distinct doublewords in storage. The first and second operands are fetched into bits 0-63 of the even-odd general register pair designated by the  $R_3$  field of the instruction; the first operand is fetched into the even-numbered register, and the second operand is fetched into the odd-numbered register.

The condition code is set based on whether the pair of doublewords were fetched without alteration by other CPUs or the channel subsystem. CC0 means that neither doubleword was altered during the fetching; CC3 means that one of the doublewords was altered.

The load-and-store-on-condition facility provides a means of executing a load or store, subject to the control of the condition code. Therefore, no branch instruction(s) are necessary to select the various code paths that effect the loading or storing. Consider the following code fragment that implements a min() function for four storage parameters:

|   | LG  | 15,PARM1 |

|---|-----|----------|

|   | CG  | 15,PARM2 |

|   | JNL | A        |

|   | LG  | 15,PARM2 |

| A | CG  | 15,PARM3 |

|   | JNL | В        |

|   | LG  | 15,PARM3 |

| В | CG  | 15,PARM4 |

|   | JNL | С        |

|   | LG  | 15,PARM4 |

| С |     |          |

With the load-and-store-on-condition facility, equivalent function can be realized without all the branching instructions, as follows

| LG   | 15,PARM1         |     |       |           |

|------|------------------|-----|-------|-----------|

| CG   | 15,PARM2         |     |       |           |

| LOCG | 15,PARM2,B'0100' | (or | LOCGL | 15,PARM2) |

| CG   | 15, PARM3        |     |       |           |

| LOCG | 15,PARM3,B'0100' | (or | LOCGL | 15,PARM3) |

| CG   | 15,PARM4         |     |       |           |

| LOCG | 15,PARM4,B'0100' | (or | LOCGL | 15,PARM4) |

|      |                  |     |       |           |

| Instruction                                                                          | Mnemonic              | OpCode        | 1 <sup>st</sup> Operand | 2 <sup>nd</sup> Operand | 3 <sup>rd</sup> Operand |

|--------------------------------------------------------------------------------------|-----------------------|---------------|-------------------------|-------------------------|-------------------------|

| LOAD ON CONDITION                                                                    | LOCR                  | B9F2          | R <sub>1</sub> .32-63   | R <sub>2</sub> .32-63   | Condition Mask          |

| LOAD ON CONDITION                                                                    | LOCGR                 | B9E2          | R <sub>1</sub> .0-63    | R <sub>2</sub> .0-63    | Condition Mask          |

| LOAD ON CONDITION                                                                    | LOC                   | EBF2          | R <sub>1</sub> .32-63   | S20 [32 bits]           | Condition Mask          |

| LOAD ON CONDITION                                                                    | LOCG                  | EBE2          | R <sub>1</sub> .0-63    | S20 [64 bits]           | Condition Mask          |

| STORE ON CONDITION                                                                   | STOC                  | EBF3          | R <sub>1</sub> .32-63   | S20 [32 bits]           | Condition Mask          |

| STORE ON CONDITION                                                                   | STOCG                 | EBE3          | R <sub>1</sub> .0-63    | S20 [64 bits]           | Condition Mask          |

| Explanation:<br>R <sub>n</sub> Register operand 'n'<br>S20 Storage operand designate | ed by base register v | vith 20-bit s | igned long dis          | placement               |                         |

For LOAD ON CONDITION, there are two forms of second operand: one source is a register and the other is a storage operand. For STORE ON CONDITION, the second operand is a storage operand. For each of these, there is an instruction that operates on 32-bit values and one that operates on 64-bit values.

As noted on the previous slide, the High-Level Assembler implements extended mnemonics for the load-and-store-on-condition facility. The extended mnemonic is formed by adding a suffix to one of the six basic mnemonics. When an extended mnemonic is coded, the conditional mask operand (the  $M_3$  field) is not coded.

The extended mnemonics represent the conditions that would be expected after a comparison operation: E, H, L, NE, NH, and NL. As the expected usage is following a compare instruction, HLASM does not provide extended mnemonics for other conditions (particularly CC3). However, the programmer can specify these conditions by using the  $M_3$  field.

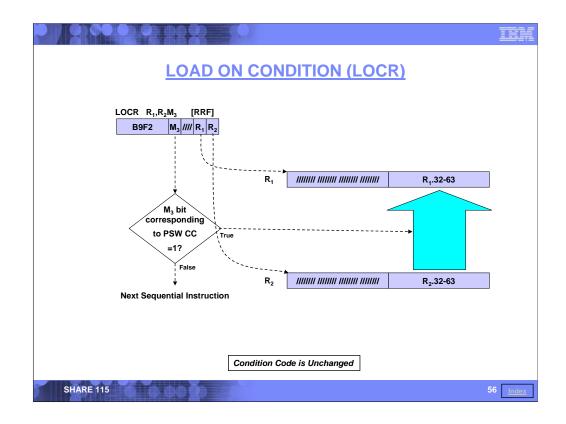

This slide illustrates the operation of LOAD ON CONDITION (LOCR).

If the condition specified in the  $M_3$  field of the instruction (or specified by the extended mnemonic) is true, bits 32-63 of the general register specified by the  $R_2$  field of the instruction are copied into the corresponding bits of the general register specified by the  $R_1$  field; bits 0-31 of the register specified by the  $R_1$  field remain unchanged.

If the condition specified by the  $M_3$  field (or extended mnemonic) is not true, all bits in the general register specified by the  $R_1$  field remain unchanged.

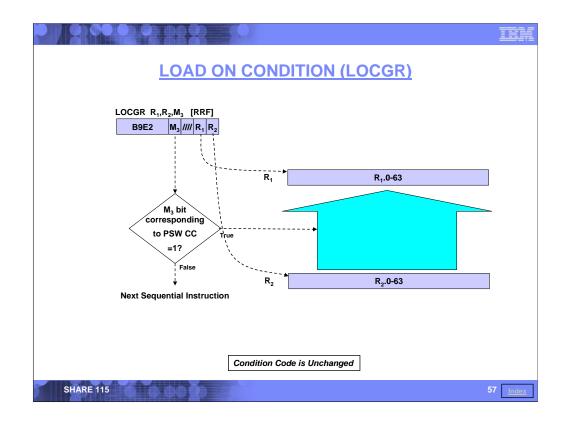

This slide illustrates the operation of LOAD ON CONDITION (LOCGR).

If the condition specified in the  $M_3$  field of the instruction (or specified by the extended mnemonic) is true, bits 0-63 of the general register specified by the  $R_2$  field of the instruction are copied into the corresponding bits of the general register specified by the  $R_1$  field.

If the condition specified by the  $M_3$  field (or extended mnemonic) is not true, all bits in the general register specified by the  $R_1$  field remain unchanged.

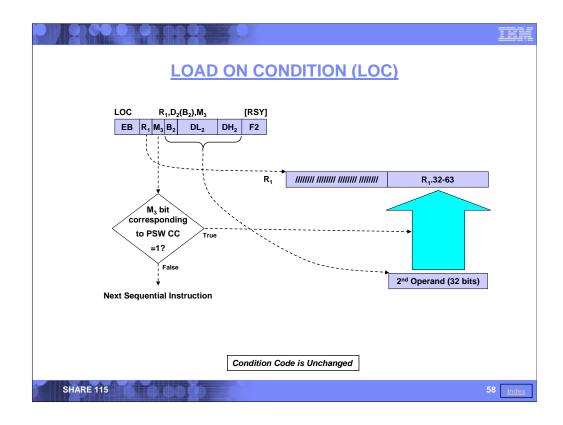

This slide illustrates the operation of LOAD ON CONDITION (LOC).

If the condition specified in the  $M_3$  field of the instruction (or specified by the extended mnemonic) is true, the four bytes designated by the second-operand location are copied into bits 32-63 of the general register specified by the  $R_1$  field; bits 0-31 of the register remain unchanged.

If the condition specified by the  $M_3$  field (or extended mnemonic) is not true, all bits in the general register specified by the  $R_1$  field remain unchanged.

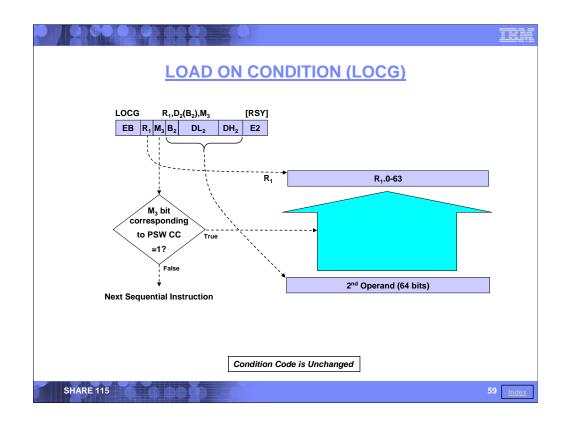

This slide illustrates the operation of LOAD ON CONDITION (LOCG).

If the condition specified in the  $M_3$  field of the instruction (or specified by the extended mnemonic) is true, the eight bytes designated by the second-operand location are copied into bits 0-63 of the general register specified by the  $R_1$  field.

If the condition specified by the  $\rm M_3$  field (or extended mnemonic) is not true, all bits in the general register specified by the  $\rm R_1$  field remain unchanged.

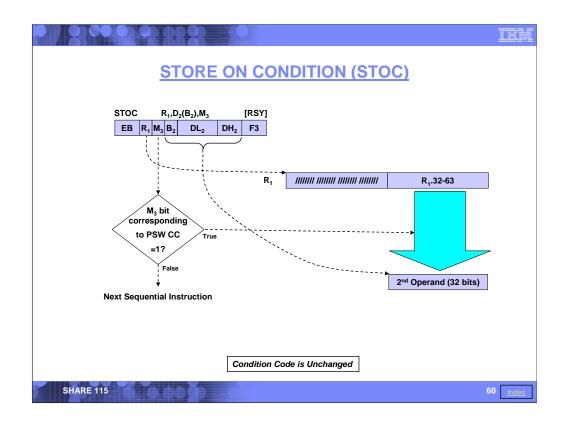

This slide illustrates the operation of STORE ON CONDITION (STOC).

If the condition specified in the  $M_3$  field of the instruction (or specified by the extended mnemonic) is true, bits 32-63 of the general register specified by the  $R_1$  field are stored at the four-byte second-operand location.

If the condition specified by the  $\rm M_3$  field (or extended mnemonic) is not true, no store operation occurs.

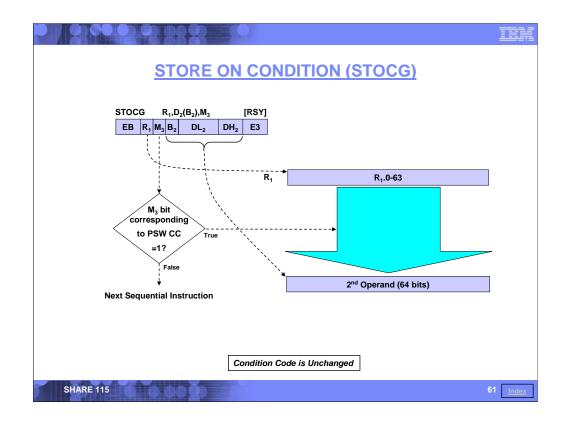

This slide illustrates the operation of STORE ON CONDITION (STOCG).

If the condition specified in the  $M_3$  field of the instruction (or specified by the extended mnemonic) is true, bits 0-63 of the general register specified by the  $R_1$  field are stored at the eight-byte second-operand location

If the condition specified by the  $\rm M_3$  field (or extended mnemonic) is not true, no store operation occurs.

|           |                                      |                                               | IBM             |

|-----------|--------------------------------------|-----------------------------------------------|-----------------|

|           | Distinct-Ope                         | rands Facility (1)                            |                 |

| Suite     | of instructions to provide nond      | lestructive analogs to existing destructive   |                 |

| instru    | uctions                              |                                               |                 |

| •         | Target register is separate from sou | Irce registers                                |                 |

| •         | Nondestructive instructions provide  | ed for:                                       |                 |

|           | ADD                                  | OR                                            |                 |

|           | ADD LOGICAL                          | SHIFT LEFT                                    |                 |

|           | ADD LOG. w/SIGN. IMMED.              | SHIFT RIGHT                                   |                 |

|           | AND                                  | SUBTRACT                                      |                 |

|           | EXCLUSIVE OR                         | SUBTRACT LOGICAL                              |                 |

| Inten     | ded to provide register-constrai     | nt relief for compilers                       |                 |

| Instal    | llation of the distinct-operands     | facility (& al.) indicated by facility bit 45 |                 |

|           |                                      |                                               |                 |

|           |                                      |                                               |                 |

|           |                                      |                                               |                 |

|           |                                      |                                               |                 |

|           |                                      |                                               |                 |

| SHARE 115 | C COLORD                             |                                               | 62 <u>Index</u> |

Beginning with the original System/360, the architecture has a long tradition of performing arithmetic or logical operations on two source operands, and then replacing one of the source operands with the result. This was completely understandable for RR-format instructions, where the instruction format only had room for two registers.

With the advent of newer instruction formats, there is sufficient space for separate source and target operand specifications. z/Architecture began exploiting this with the 64-bit shift operations, and the decimal-floating-point facility extended the practice by having the results of floating point computations placed in a register that can be distinct from the two source registers.

Having a separate destination operand register provides greater flexibility to compiler designers and assembler programmers. When a source operand needs to be preserved, extra instructions are not needed to perform a copying operation.

The distinct-operands facility introduces a series of arithmetic and logical instructions that have a result register that can be distinct from any of the source operands. For all of the instructions, the first (result) and third (source) operands are in a register; depending on the instruction, the second operand is a register, immediate field, or storage-type operand.

All of the distinct-operand-facility instructions have a suffix of "K" in the mnemonic.

| DD                               |         |      | 1 1                   | 2 <sup>nd</sup> Operand | 3 <sup>rd</sup> Operand |

|----------------------------------|---------|------|-----------------------|-------------------------|-------------------------|

|                                  | ARK     | B9F8 | R <sub>1</sub> .32-63 | R <sub>2</sub> .32-63   | R <sub>3</sub> .32-63   |

| DD                               | AGRK    | B9E8 | R <sub>1</sub> .0-63  | R <sub>2</sub> .0-63    | R <sub>3</sub> .0-63    |

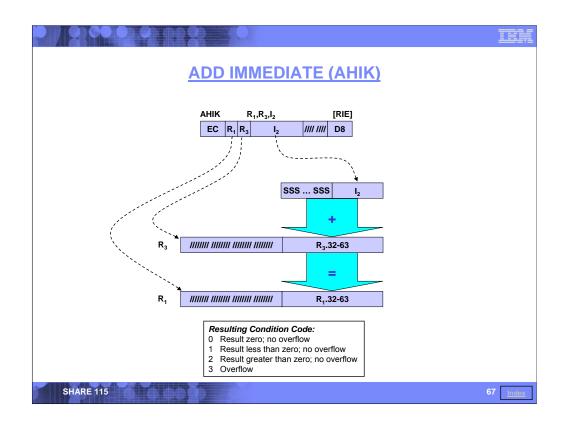

| DD IMMEDIATE                     | AHIK    | ECD8 | R <sub>1</sub> .32-63 | l <sub>2</sub>          | R <sub>3</sub> .32-63   |

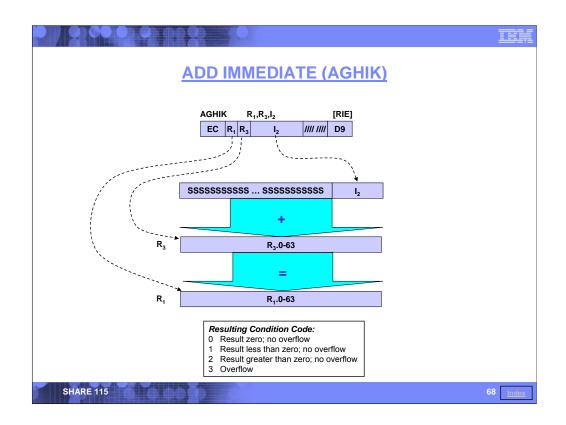

| DD IMMEDIATE                     | AGHIK   | ECD9 | R <sub>1</sub> .0-63  | I <sub>2</sub>          | R <sub>3</sub> .0-63    |

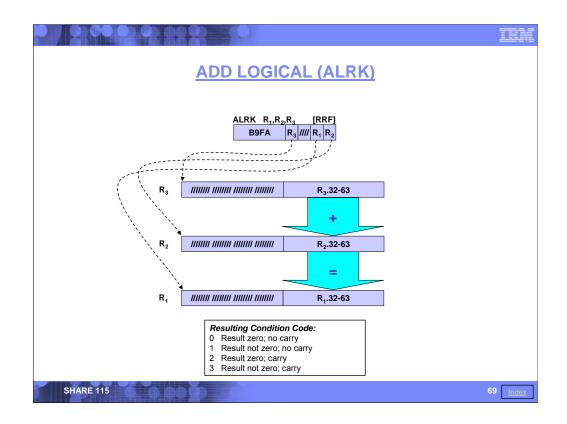

| DD LOGICAL                       | ALRK    | B9FA | R <sub>1</sub> .32-63 | R <sub>2</sub> .32-63   | R <sub>3</sub> .32-63   |

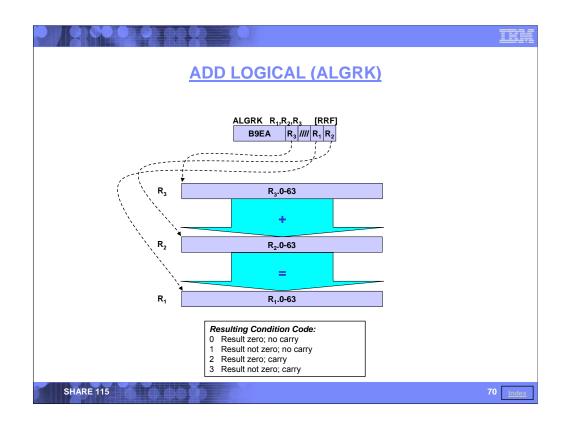

| DD LOGICAL                       | ALGRK   | B9EA | R <sub>1</sub> .0-63  | R <sub>2</sub> .0-63    | R <sub>3</sub> .0-63    |

| DD LOGICAL WITH SIGNED IMMEDIATE | ALHSIK  | ECDA | R <sub>1</sub> .32-63 | I <sub>2</sub>          | R <sub>3</sub> .32-63   |

| DD LOGICAL WITH SIGNED IMMEDIATE | ALGHSIK | ECDB | R <sub>1</sub> .0-63  | I <sub>2</sub>          | R <sub>3</sub> .0-63    |

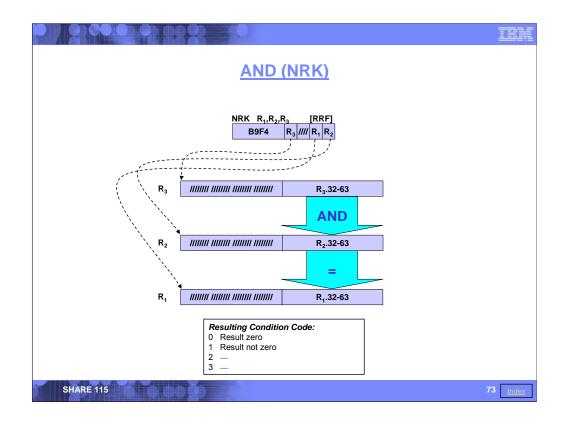

| ND                               | NRK     | B9F4 | R <sub>1</sub> .32-63 | R <sub>2</sub> .32-63   | R <sub>3</sub> .32-63   |

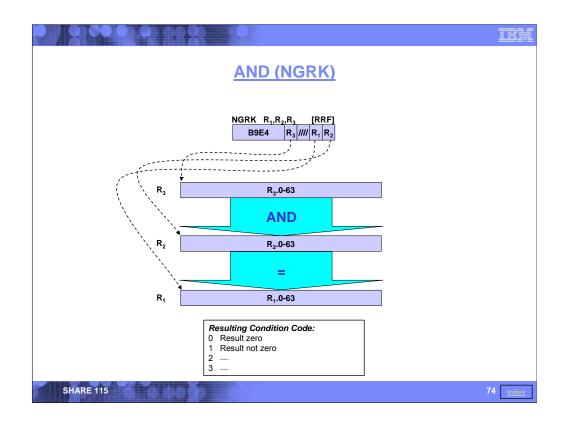

| ND                               | NGRK    | B9E4 | R <sub>1</sub> .0-63  | R <sub>2</sub> .0-63    | R <sub>3</sub> .0-63    |

This slide introduces the various ADD and AND instructions in the distinct-operand facility.

For the ADD instructions, the second operand is either a register or immediate field. For the AND, OR, and XOR instructions, the second operand is always a register.

| nstruction                 | Mnemonic | OpCode | 1 <sup>st</sup> Operand | 2 <sup>nd</sup> Operand | 3 <sup>rd</sup> Operand |

|----------------------------|----------|--------|-------------------------|-------------------------|-------------------------|

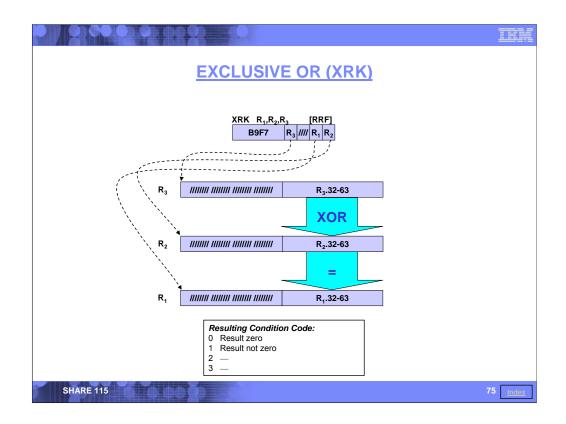

| EXCLUSIVE OR               | XRK      | B9F7   | R <sub>1</sub> .32-63   | R <sub>2</sub> .32-63   | R <sub>3</sub> .32-63   |

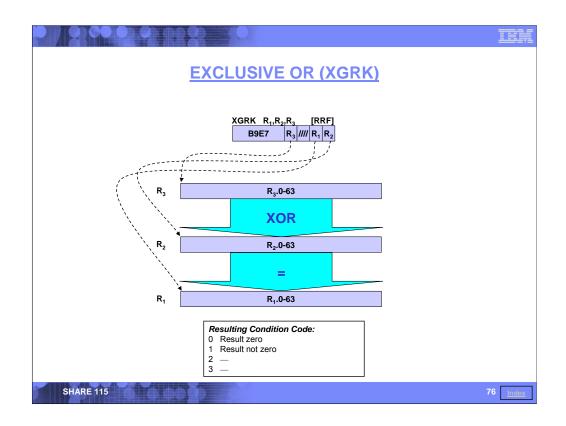

| EXCLUSIVE OR               | XGRK     | B9E7   | R₁.0-63                 | R <sub>2</sub> .0-63    | R <sub>3</sub> .0-63    |

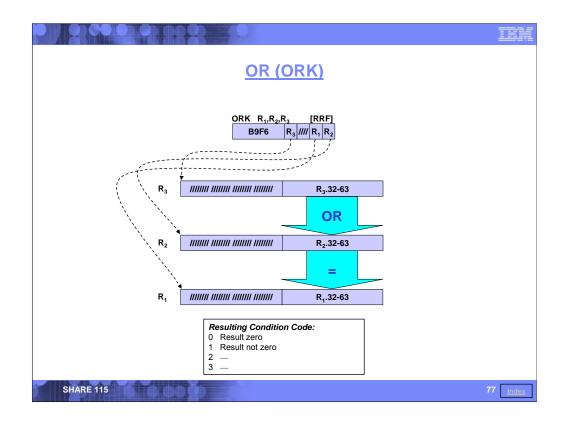

| DR                         | ORK      | B9F6   | R₁.32-63                | R <sub>2</sub> .32-63   | R <sub>3</sub> .32-63   |

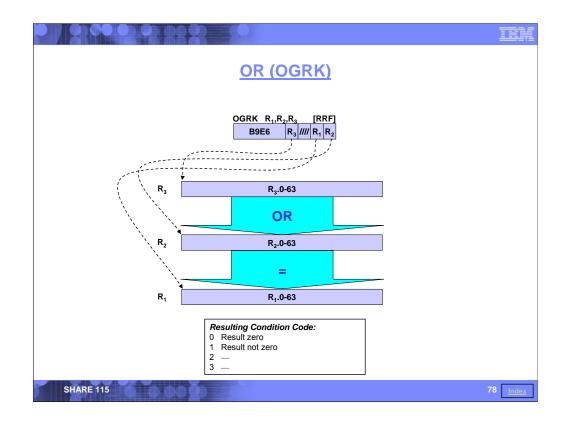

| DR                         | OGRK     | B9E6   | R <sub>1</sub> .0-63    | R <sub>2</sub> .0-63    | R <sub>3</sub> .0-63    |

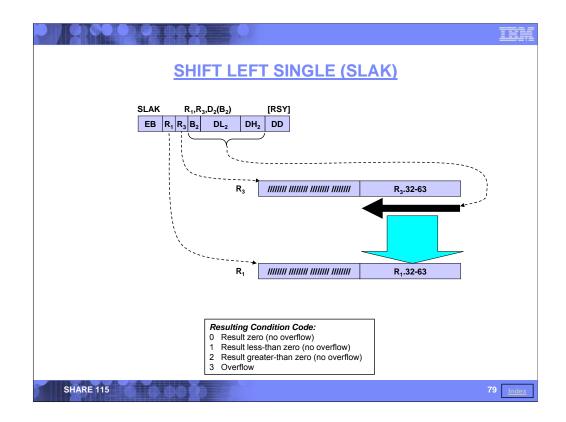

| SHIFT LEFT SINGLE          | SLAK     | EBDD   | R <sub>1</sub> .32-63   | S20                     | R <sub>3</sub> .32-63   |

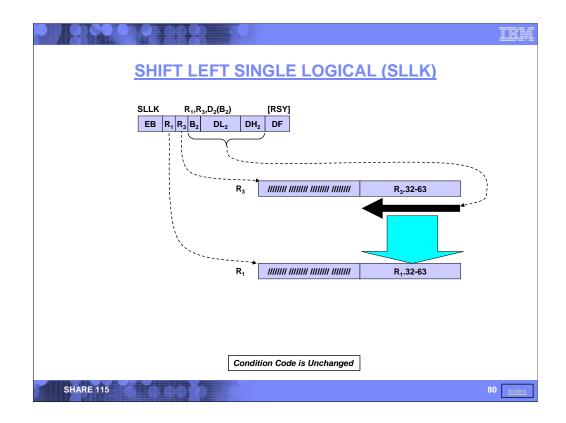

| SHIFT LEFT SINGLE LOGICAL  | SLLK     | EBDF   | R <sub>1</sub> .32-63   | S20                     | R <sub>3</sub> .32-63   |

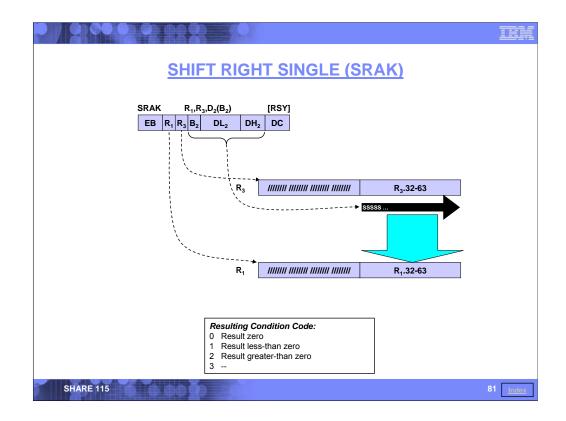

| SHIFT RIGHT SINGLE         | SRAK     | EBDC   | R <sub>1</sub> .32-63   | S20                     | R <sub>3</sub> .32-63   |

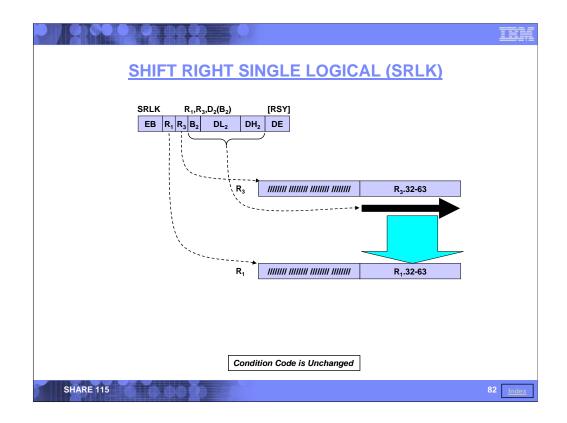

| SHIFT RIGHT SINGLE LOGICAL | SRLK     | EBDE   | R <sub>1</sub> .32-63   | S20                     | R <sub>3</sub> .32-63   |

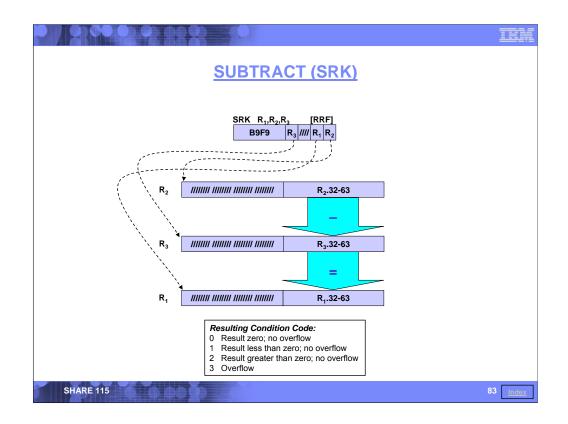

| SUBTRACT                   | SRK      | B9F9   | R <sub>1</sub> .32-63   | R <sub>2</sub> .32-63   | R <sub>3</sub> .32-63   |

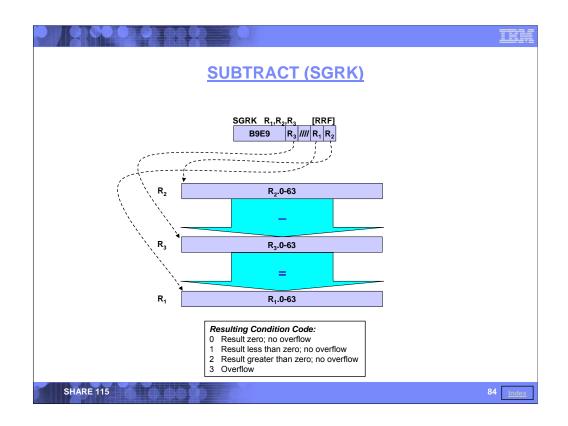

| SUBTRACT                   | SGRK     | B9E9   | R <sub>1</sub> .0-63    | R <sub>2</sub> .0-63    | R <sub>3</sub> .0-63    |

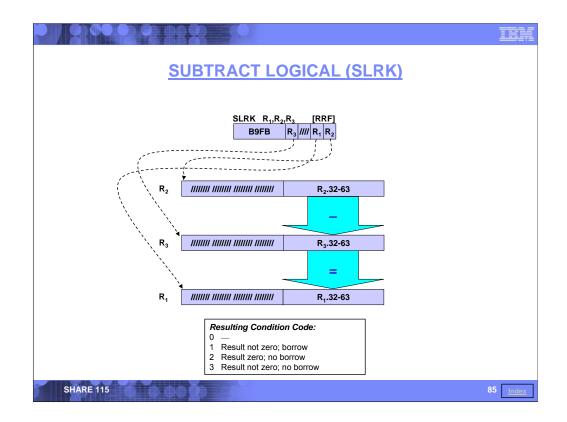

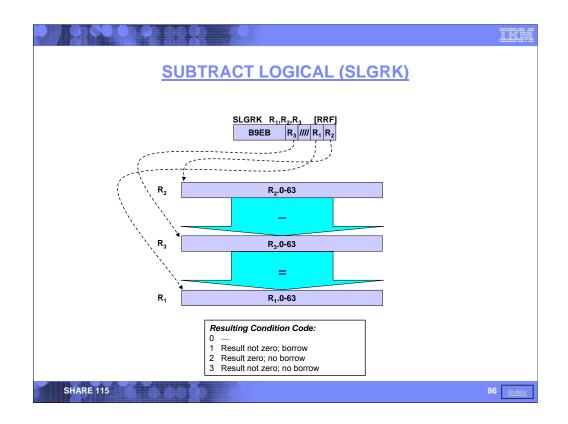

| SUBTRACT LOGICAL           | SLRK     | B9FB   | R <sub>1</sub> .32-63   | R <sub>2</sub> .32-63   | R <sub>3</sub> .32-63   |

| SUBTRACT LOGICAL           | SLGRK    | B9EB   | R <sub>1</sub> .0-63    | R <sub>2</sub> .0-63    | R <sub>3</sub> .0-63    |

This slide enumerates the remaining instructions in the distinct-operand facility.

For the SHIFT instructions, the second operand is not used to access storage; rather, the rightmost six bits of the second-operand address form the shift amount (just like any other shift operation).

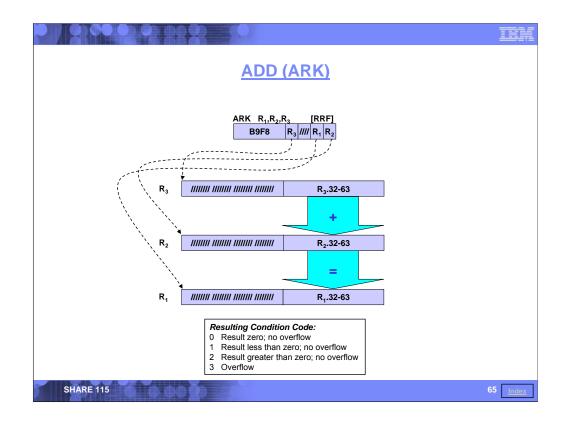

For ADD (ARK), the second operand is added to the third operand, and the result is placed in the first operand. Each operand occupies the rightmost 32 bits (bits 32-63) of the general register designated by the corresponding R field of the instruction.

Unless the R<sub>1</sub> field designates the same register as the R<sub>2</sub> or R<sub>3</sub> field, the contents of the general registers designated by the R<sub>2</sub> and R<sub>3</sub> fields remain unchanged. The contents of bit positions 0-31 of the general register designated by the R<sub>1</sub> field always remains unchanged.

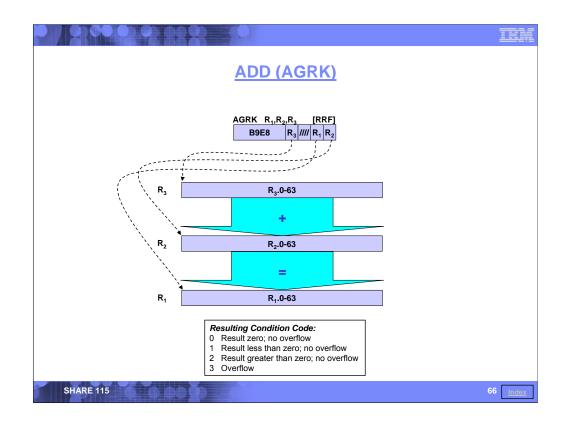

For ADD (AGRK), the second operand is added to the third operand, and the result is placed in the first operand. Each operand occupies all 64 bits of the general register designated by the corresponding R field of the instruction.

Unless the R<sub>1</sub> field designates the same register as the R<sub>2</sub> or R<sub>3</sub> field, the contents of the general registers designated by the R<sub>2</sub> and R<sub>3</sub> fields remain unchanged.